AD484 user manual

V1.2

AD484 User manual

February 2007

www.4dsp.com

- 4 -

1 Acronyms and related documents

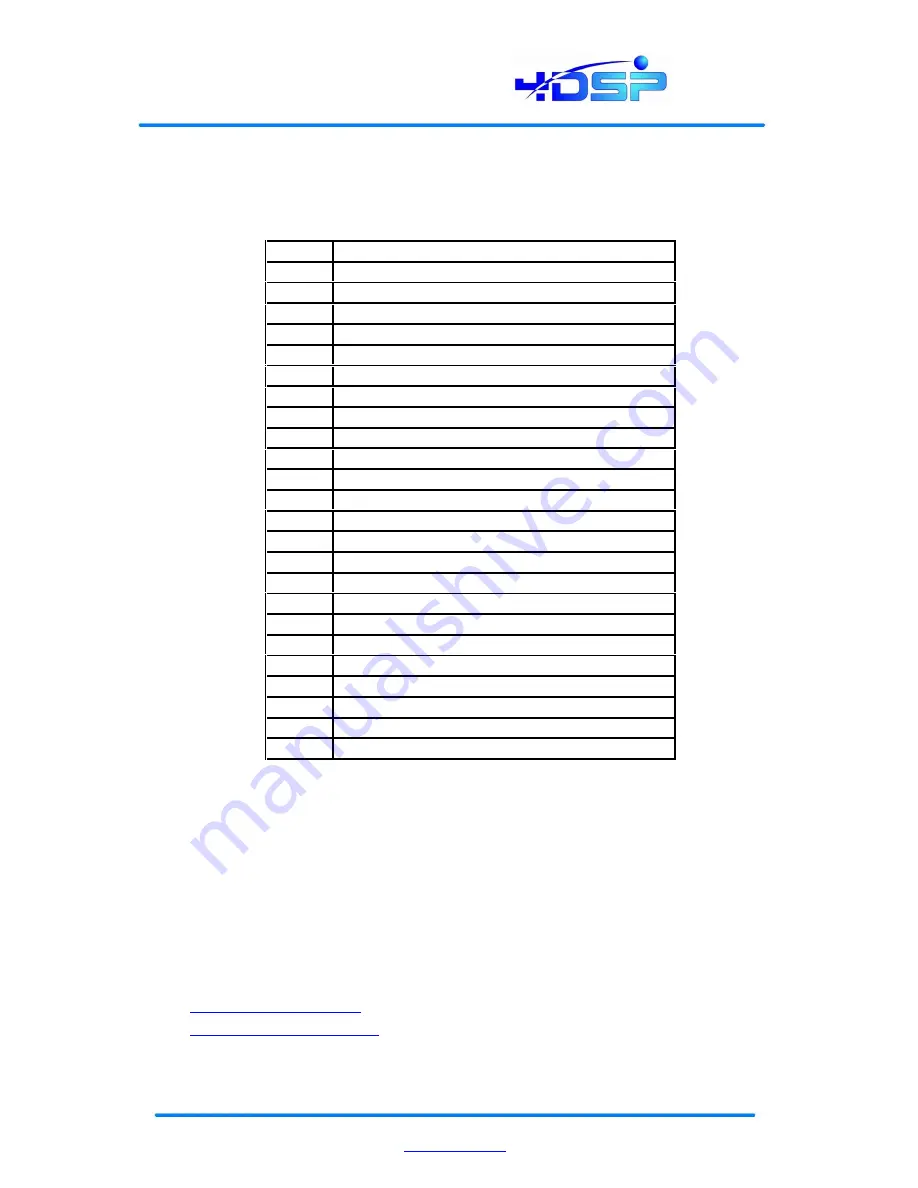

1.1 Acronyms

ADC

Analog to Digital Converter

DAC

Digital to Analog Converter

DCI

Digitally Controlled Impedance

DDR

Double Data Rate

DSP

Digital Signal Processing

EPROM Erasable Programmable Read-Only Memory

FBGA

Fineline Ball Grid Array

FPDP

Front Panel Data Port

FPGA

Field Programmable Gate Array

JTAG

Join Test Action Group

LED

Light Emitting Diode

LVTTL

Low Voltage Transistor Logic level

LVDS

Low Differential Data Signaling

LSB

Least Significant Bit(s)

LVDS

Low Voltage Differential Signaling

MGT

Multi-Gigabit Transceiver

MSB

Most Significant Bit(s)

PCB

Printed Circuit Board

PCI

Peripheral Component Interconnect

PCI-e

PCI Express

PLL

Phase Locked Loop

PMC

PCI Mezzanine Card

QDR

Quadruple Data rate

SDRAM

Synchronous Dynamic Random Access memory

SRAM

Synchronous Random Access memory

Table 1: Glossary

1.2 Related Documents

IEEE Std 1386.1-2001 : IEEE Standard Physical and Environmental Layers for PCI

Mezzanine Cards (PMC).

ANSI/VITA 32-2003 : Processor PMC.

ANSI/VITA 39-2003 : PCI-X for PMC and Processor PMC.

ANSI/VITA 42.0-2005 : XMC Switched Mezzanine Card Auxiliary Standard.

IEEE Std 1386-2001 : IEEE Standard for a Common Mezzanine Card (CMC) Family.

Xilinx Virtex-4 user guide

Xilinx PCI-X core datasheet

Xilinx Virtex-4 Rocket I/O guide