AD484 user manual

V1.2

AD484 User manual

February 2007

www.4dsp.com

- 8 -

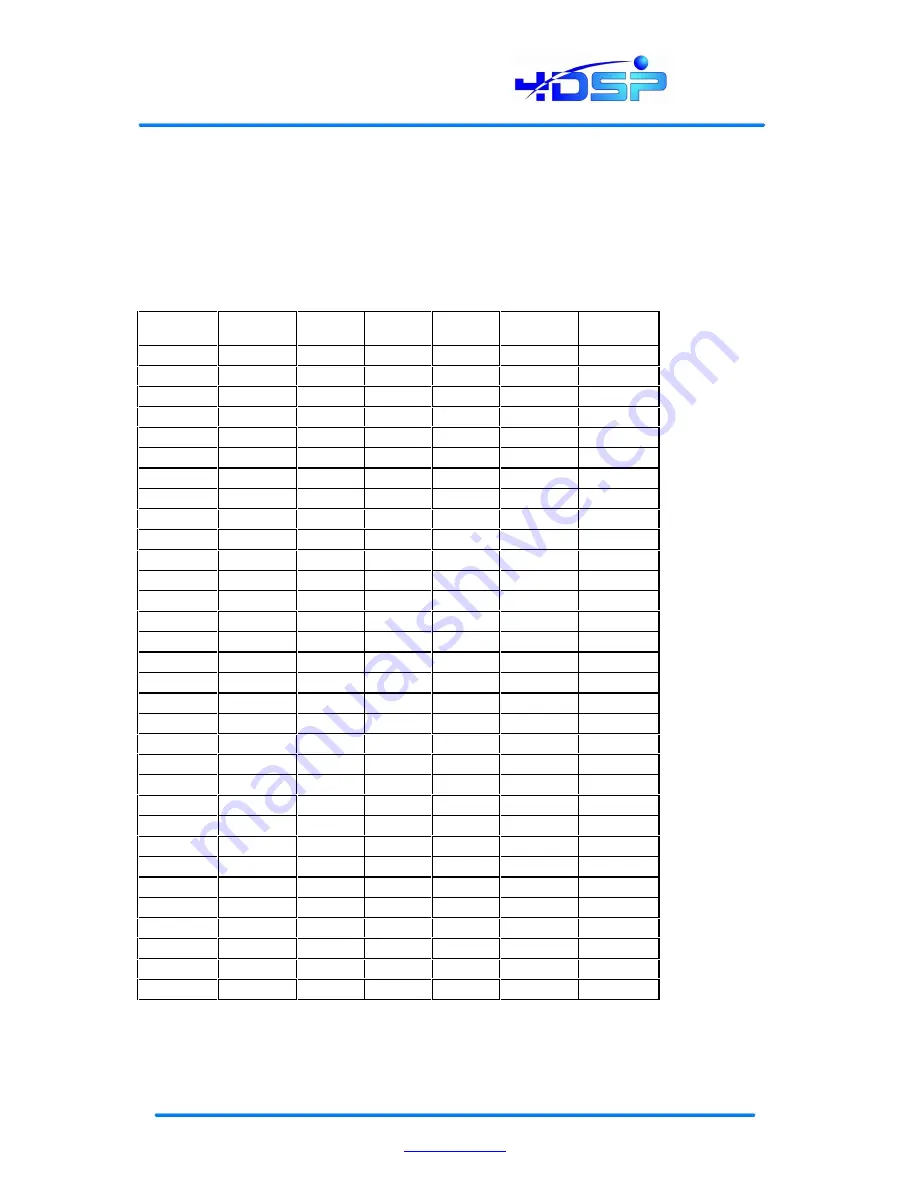

3.1.1.6

Pn4 user I/O connector

The Pn4 connector is wired to the Virtex-4 device A. The 32 lower bits are available only if an

XC4VFX60 device is mounted on board. The 32 higher bits are available only if PCI 32-bit is

used and only if specified at the time of order.

All signals are user-defined 3.3V LVTLL./LVCMOS.

Connector

pin

Signal

name

FPGA

pin

FPGA

pin

Signal

name

Connector

pin

1

Pn4_IO0

M9

M10

Pn4_IO1

2

3

Pn4_IO2

N11

M11

Pn4_IO3

4

5

Pn4_IO4

N7

N8

Pn4_IO5

6

7

Pn4_IO6

N6

P6

Pn4_IO7

8

9

Pn4_IO8

P10

P11

Pn4_IO9

10

11

Pn4_IO10 P9

N9

Pn4_IO11

12

13

Pn4_IO12 R8

P8

Pn4_IO13

14

15

Pn4_IO14 R6

R7

Pn4_IO15

16

17

Pn4_IO16 N21

M21

Pn4_IO17

18

19

Pn4_IO18 M20

M19

Pn4_IO19

20

21

Pn4_IO20 P19

N19

Pn4_IO21

22

23

Pn4_IO22 N18

N17

Pn4_IO23

24

25

Pn4_IO24 P16

N16

Pn4_IO25

26

27

Pn4_IO26 R18

P18

Pn4_IO27

28

29

Pn4_IO28 P21

P20

Pn4_IO29

30

31

Pn4_IO30 R17

R16

Pn4_IO31

32

33

Pn4_IO32 L9

M5

Pn4_IO33

34

35

Pn4_IO34 L5

AD11

Pn4_IO35

36

37

Pn4_IO36 AD10

L4

Pn4_IO37

38

39

Pn4_IO38 L3

AB11

Pn4_IO39

40

41

Pn4_IO40 AC11

M4

Pn4_IO41

42

43

Pn4_IO42 N4

T9

Pn4_IO43

44

45

Pn4_IO44 T8

P5

Pn4_IO45

46

47

Pn4_IO46 R5

AA10

Pn4_IO47

48

49

Pn4_IO48 AB10

P4

Pn4_IO49

50

51

Pn4_IO50 R3

W10

Pn4_IO51

52

53

Pn4_IO52 Y10

N3

Pn4_IO53

54

55

Pn4_IO54 P3

U6

Pn4_IO55

56

57

Pn4_IO56 U5

T4

Pn4_IO57

58

59

Pn4_IO58 T3

U7

Pn4_IO59

60

61

Pn4_IO60 V6

U4

Pn4_IO61

62

63

Pn4_IO62 V4

U9

Pn4_IO63

64

Table 2 : Pn4 pin assignment