UM008 FMC204 User Manual

r1.14

UM008

- 13 -

5

R

x

/5

T

x

5

R

x

/5

T

x

5

R

x

/5

T

x

5

R

x

/5

T

x

5

R

x

/5

T

x

5

R

x

/5

T

x

5

R

x

/5

T

x

5

R

x

/5

T

x

5

R

x

/5

T

x

5

R

x

/5

T

x

Figure 5: MGT interconnect topologies

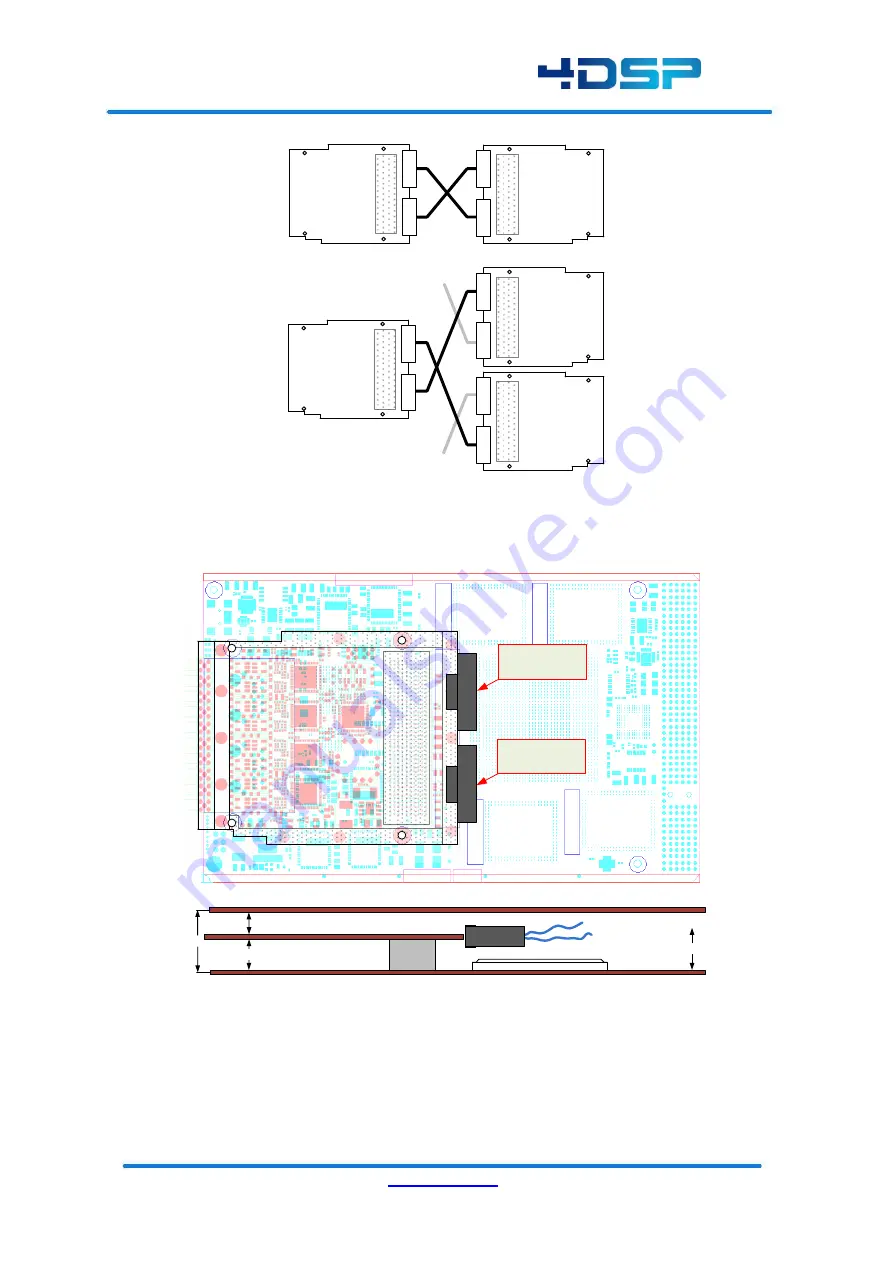

FMC

2

0

,3

2

1

0

.0

0

7

.1

2

1

3

.7

1

FPGA

MICTOR 2

Rx-Tx 5-9

MICTOR 1

Rx-Tx 0-4

TOP VIEW

Figure 6: 4DSP CPCI board stack (slot-to-slot)