42 CPCI-7806/CPCI-7806RC Pentium/Celeron M Universal CompactPCI Single Board Computer

Publication No. 500-657806-000 Rev. G

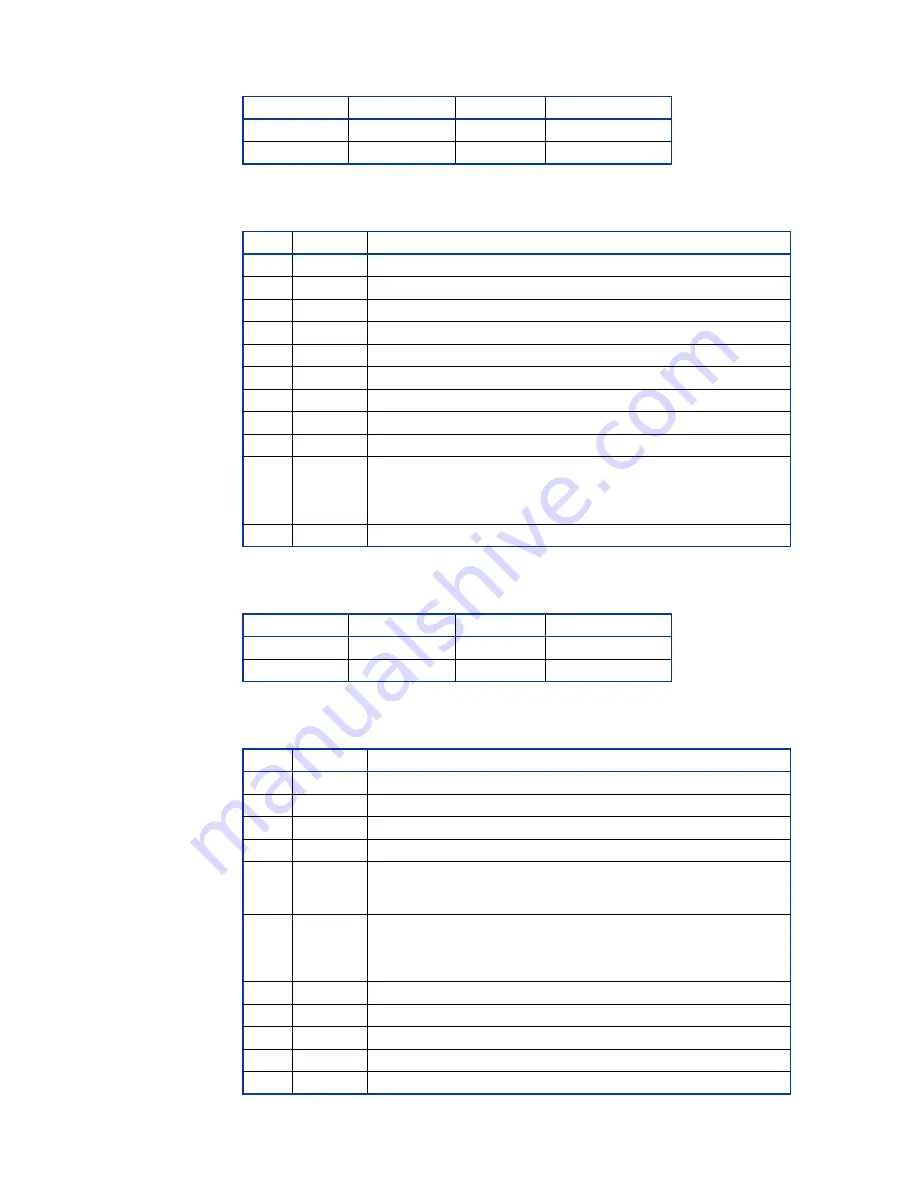

Table 3-5 Command Register (COM)

Offset

04-05h

Attribute

Read/Write

Default Value

000Ah

Size

16 bit

Lockable

No

Power Well

Core

Table 3-6 Details of Command Register (COM)

Bit

Attribute

Description

15:10

N/A

Reserved

9

RO

FBE - Fast Back to Back Enable: Reserved as ‘0’. Read Only

8

RO

SERR# Enable: Reserved as ‘0’. Read Only

7

RO

Wait Cycle Control: Reserved as ‘0’. Read Only

6

RO

Parity error response: Reserved as ‘0’. Read Only

5

RO

VGA Palette Snoop: Reserved as ‘0’. Read Only

4

RO

PMWE - Postable Memory Write Enable: Reserved as ‘0’. Read Only

3

RO

SCE - Special Cycle Enable: Reserved as ‘0’. Read Only

2

RO

BME - Bus Master Enable: Reserved as ‘0’. Read Only

1

R/W

MSE - Memory Space Enable: This bit controls access to the WDT’s Memory

Mapped registers. If this bit is set, accesses to the WDT’s Memory Mapped

registers are enabled. The Base Address register for WDT should be

programmed before this bit is set.

0

RO

IOSE - I/O Space Enable: Reserved as ‘0’. Read Only

Table 3-7 Device Status Register (DS)

Offset

06h - 07h

Attribute

Read/Write Clear

Default Value

0280h

Size

16 bit

Lockable

No

Power Well

Core

Table 3-8 Details of Device Status Register (DS)

Bit

Attribute

Description

15

RO

DPE - Detected Parity Error: Reserved as ‘0’. Read Only

14

RO

SSE - Signaled System Error: Reserved as ‘0’. Read Only

13

RO

RMA - Received Master Abort: Reserved as ‘0’. Read Only

12

RO

RTA - Received Target Abort: Reserved as ‘0’. Read Only

11

R/WC

STA - Signaled Target-Abort Status: This bit is set when the function is

targeted with a transaction that Hance Rapids ICH terminates with a target

abort. Software resets STA to 0 by writing a 1 to this bit location.

10:9

RO

DEVT - DEVSEL# Timing Status: This 2-bit field defines the timing for

DEVSEL# assertion. These read only bits indicate Hance Rapids ICH’s

DEVSEL# timing when performing a positive decode. Note: Hance Rapids ICH

generates DEVSEL# with medium time.

8

RO

Data Parity error Detected: Reserved as ‘0’. Read Only

7

RO

Fast Back-to-Back Capable: Reserved as ‘1’. Read Only

6

RO

UDF - User Definable Features: Reserved as ‘0’. Read Only

5

RO

66 MHz Capable: Reserved as ‘0’. Read Only

4:0

RO

Reserved. Read Only