62 PPC11A 6U VME Single Board Computer

Publication No. PPC11A-HRM/1

4.23

Resets and Interrupts

The Programmable Interrupt Controller within the processor controls resets and

interrupts to the processing cores.

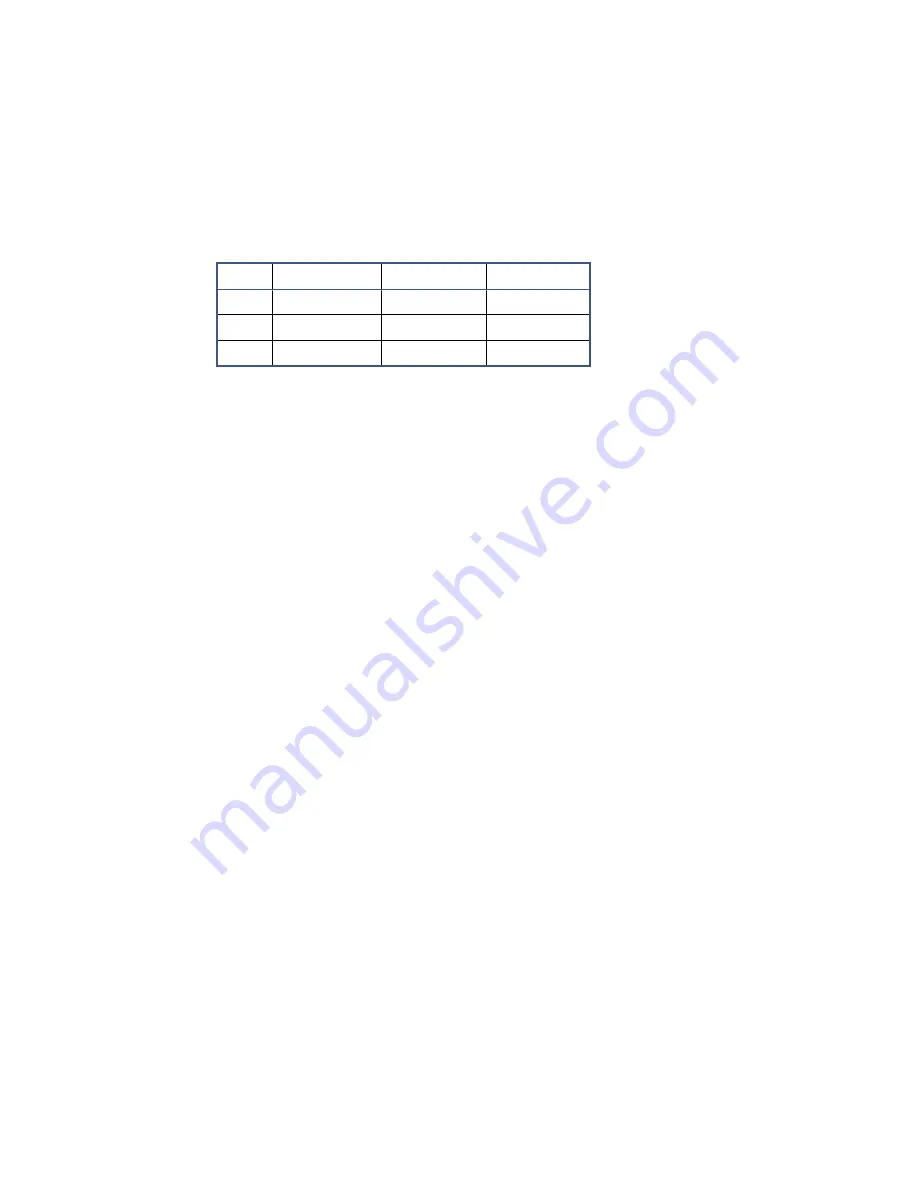

The following table shows the various external interrupt sources to the Interrupt

Controller and their relative priorities. It also shows whether the previous state of

the processor is recoverable.

Table 4-31 External Interrupt Inputs to Processor

Priority Interrupt

Cause

Recoverability

0

Power-on reset

PORESET~ input Non-recoverable

1

Hard Reset Input

HRESET~ input

Non-recoverable

2

External Interrupt IRQ~ inputs

Recoverable

The FPGA contains all the required logic for resets and interrupts.

4.23.1 Hard Reset

A hard reset, generated by the FPGA, is used to reset the processor (including the

cores) and all other devices on the PPC11A that require resetting.

A hard reset is asserted when any of the following events occur:

•

Any of the power supplies fall outside specification

•

The VME SYSRESET~ signal is asserted

•

The processor HRESET_REQ~ output is asserted

•

The front panel Reset switch is toggled (when enabled in software)

•

The HRESET~ signal on the BDM header is asserted

•

The reset output of the BMM is asserted

•

The EXT_RESET~ backplane pin is asserted

•

The RESET_OUT~ signal from any PMC/XMC site is asserted

•

A watchdog timer expires

•

A reset is generated via an FPGA register

The duration of the internal hard reset signal is

at least 10ms.

The FPGA latches the cause of a hard reset and displays it in a

(offset 0x61B or 0x61C) for software interrogation.

When operating as the VME System Controller, the PPC11A asserts the VME

SYSRESET~ signal when a hard reset occurs.