FMC30RF User Manual

r1.3

UM015

- 18 -

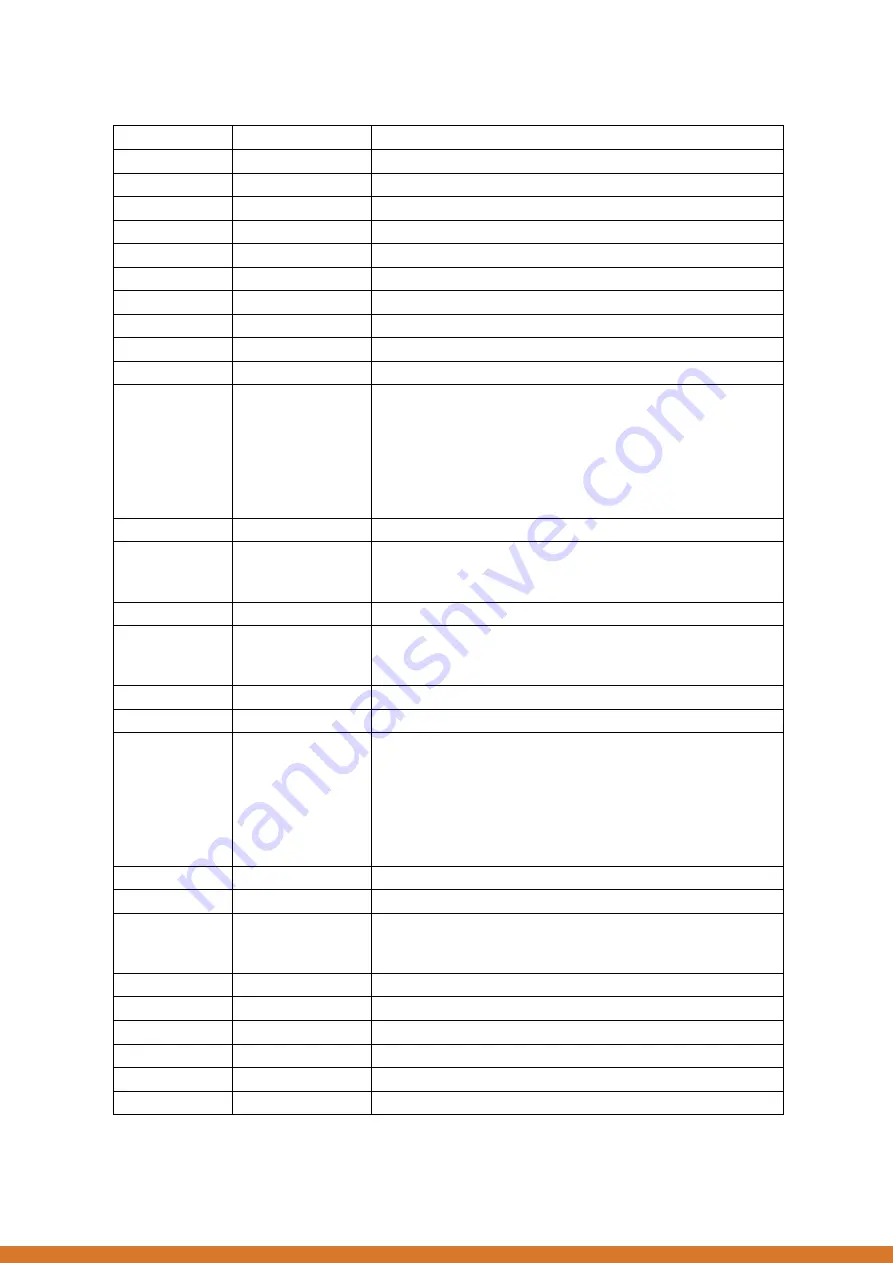

LA15_P

AFE7225_RESET

Connects to AFE7225 RESET

LA16_N

AFE7225_CS#

Connects to AFE7225 SEN

LA16_P

AFE7225_PD

Connects to AFE7225 PDN

LA17_N_CC

RF_ATT_V4

Connects to SKY12329-350LF V4

LA17_P_CC

RF_ATT_V3

Connects to SKY12329-350LF V3

LA18_N_CC

AMC7823_CS#

Connects to AMC7823 SS

LA18_P_CC

AMC7823_RESET#

Connects to AMC7823 RESET

LA19_N

CDCE62005_LOCK

Connects to CDCE62005 PLL_LOCK

LA19_P

TRF3765_LOCK

Connects to TRF3765 LD

LA20_N

RF_ATT_V5

Connects to SKY12329-350LF V5

LA20_P

TRF3720_LOCK

Connects to TRF3720 LD

LA21_N

SCLK

Connects to:

- CDCE62005 SPI_CLK

- TRF3765 CLOCK

- TRF3720 CLK

- TRF3711 CLOCK

- AFE7225 SCLK

- AMC7823 SCLK

LA21_P

TRF3720_CS#

Connects to TRF3720 LE

LA22_N

RX_VCO_CTRL

Behavior on RX CLK connector;

‘0’ = RX CLK connector is VCO output from TRF3765 LO4_OUT

‘1’ = RX CLK connector is VCO input to TRF3765 EXTVCO_IN

LA22_P

TRF3720_PS

Connects to TRF3720 PS

LA23_N

TX_VCO_CTRL

Behavior on TX CLK connector;

‘0’ = TX CLK connector is VCO output from TRF3720 LO_OUT

‘1’ = TX CLK connector is VCO input to TRF3720 EXT_VCO

LA23_P

TRF3711_PD#

Connects to TRF3711 CHIP_EN

LA24_N

TRF3711_CS#

Connects to TRF3711 STROBE

LA24_P

SDATA

Connects to

- CDCE62005 MOSI

- TRF3765 DATA

- TRF3720 DATA

- TRF3711 DATA

- AFE7225 SDATA

- AMC7823 MOSI

LA25_N

TRF3711_GAIN_B0

Connects to TRF3711 GAIN_B0

LA25_P

TRF3711_GAIN_B1

Connects to TRF3711 GAIN_B1

LA26_N

CDCE62005_REFEN

Behavior on on-board reference clock;

‘0’ = the on-board reference clock is powered down

‘1’ = the on-board reference clock is enabled

LA26_P

TRF3711_GAIN_B2

Connects to TRF3711 GAIN_B2

LA27_N

CDCE62005_SDOUT

Connects to CDCE62005 MISO

LA27_P

AFE7225_SDOUT

Connects to AFE7225 SDOUT

LA28_N

CDCE62005_PD#

Connects to CDCE62005 POWER_DOWN

LA28_P

CDCE62005_SYNC#

Connects to CDCE62005 SYNC

LA29_N

TRF3720_SDOUT

Connects to TRF3720 RDBK