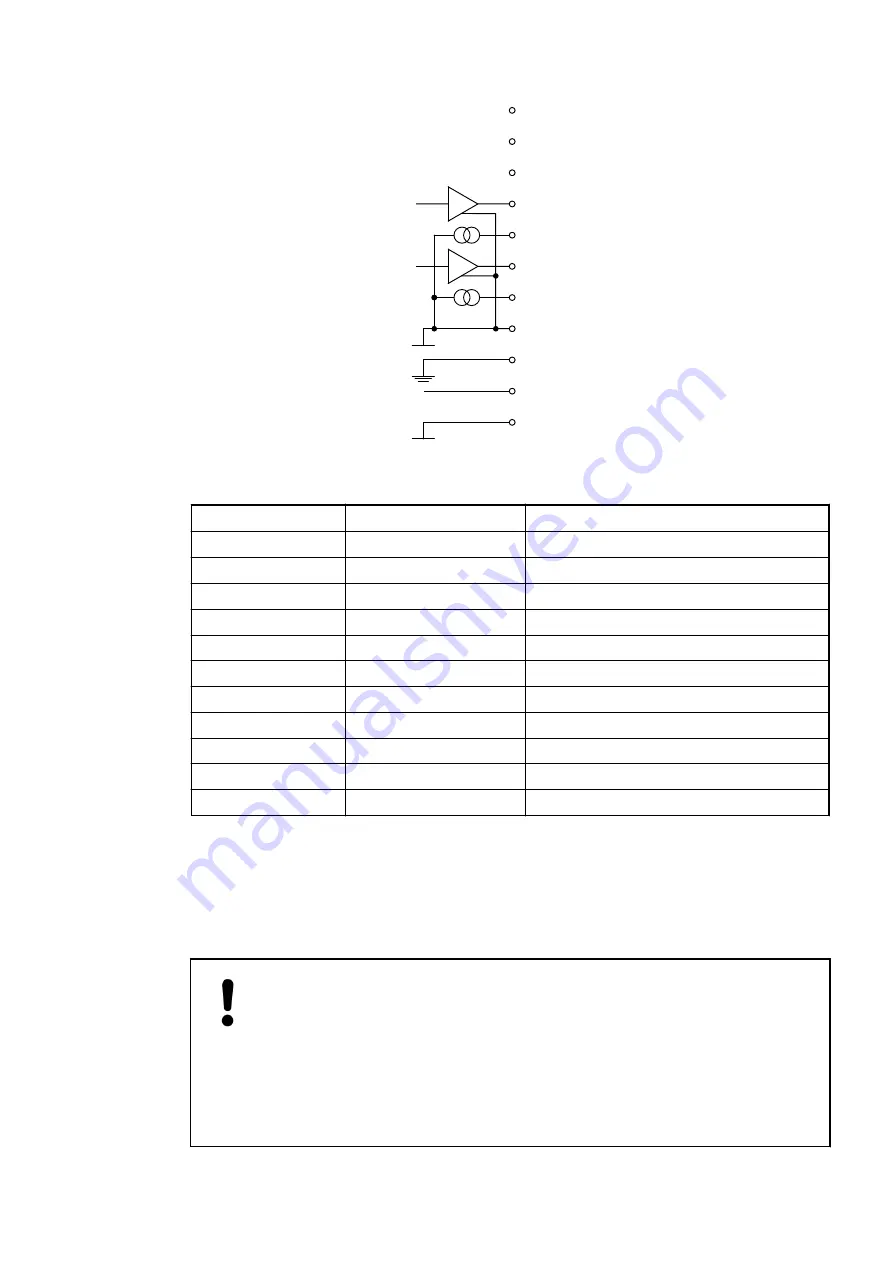

−−−

11

−−−

12

−−−

10

O0U+ 13

O0I+ 14

O1I+ 16

O01− 17

O1U+ 15

L+

19

M

20

SG

18

+

+

−

−

The assignment of the terminals:

Terminal

Signal

Description

10

---

Reserved

11

---

Reserved

12

---

Reserved

13

O0U+

Voltage output of channel 0

14

O0I+

Current output of channel 0

15

O1U+

Voltage output of channel 1

16

O1I+

Current output of channel 1

17

O01-

Negative pole of channels O0 and O1

18

SG

Shield grounding

19

L+

Process voltage L+ (24 V DC)

20

M

Process voltage M (0 V DC)

The internal power supply voltage for the module's circuitry is carried out via the I/O bus

(provided by a communication interface module or a CPU). Thus, the current consumption from

24 V DC power supply at the terminals UP/L+ and ZP/M of the CPU/communication interface

module increases by 5 mA per AO561.

The external power supply connection is carried out via the L+ (+24 V DC) and the M (0 V

DC) terminals. The M terminal is electrically interconnected to the M/ZP terminal of the CPU/

communication interface module.

NOTICE!

Risk of imprecise and faulty measurements!

Analog signals may be distorted seriously by external electromagnetic influ-

ences.

Use shielded wires when wiring analog signal sources. The cable shield must

be grounded at both ends of the cable. Provide a potential equalisation of a

low resistance to avoid high potential differences between different parts of the

plant.

Device specifications

I/O modules > Analog I/O modules

2022/01/31

3ADR010278, 3, en_US

385