Power Automation and Protection Division

I.L. 40-201.9

REL 352 Version 1.00

G-1

G

A

P

P

E

N

D

I

X

POWER SUPPLY MODULE

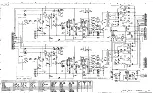

Schematic - - - - - - - - - - - - - - - - - - - - - 1356D56

Component Location Diagram - - - - - - - 1611C24

The Power Supply Module consists of two identical power supplies whose outputs are auctioneered through

diodes to provide an uninterrupted power source, in the event one of the supplies fails. The following description

is provided for one supply (both supplies are identical).

The input power from terminals J7/26AC and 28AC is applied to fuses F1 and F2, rectifier bridge BR1 and filter

network R1, C1. Therefore, both dc and ac operation are possible.

Switching transistor Q2 is turned on and off to provide current for the flywheel inductors L1 and L2 which feed

the charge capacitor C11. When transistor Q2 is turned off, the flywheel current continues through diode D5.

The dc voltage, developed across C11, is applied through resistor divider R7, R17 and R14 to the pulse width

modulator U1, pin 1. In U1, this voltage is compared with the voltage on pin 2, which is derived from an internal

Zener reference voltage on pin 16. The voltage difference between pins 1 and 2 controls the high or low duty

cycle (or pulse width) of the ac waveform on pins 12 and 13. The frequency of this ac signal is determined by

R13 and C7. This ac signal is amplified by transistor Q4 which controls the gate of switching transistor Q2 thru

driver Q3; thus completing the feedback loop which controls the voltage on capacitor C11.

Chip U1 is powered from internal element VC1 (12 volt). On powerup, VC1, is initially generated from voltage

across Zener diode Z2, driving the emitter follower Q1. VC1 also initially powers transistors Q3 and Q4 thru di-

ode D1. When the voltage across C11 gradually builds up, and overtakes VC1, transistors Q3 and Q4 will be

powered through R16 and D2. When the voltage across C11 reaches about 75% of its final value, the current

through R3 will back bias Q1 through diode D4, turning off Q1 and supplying VC1 through R3 from the voltage

across C11. This arrangement minimizes the power dissipation on Q1. For the same reason, it is extremely im-

portant to limit the current from P12V (Terminal J7 14AC) to 10mA. Otherwise, the turn off of Q1 may be ham-

pered, and serious overheating will result. The gradual buildup of voltage across C11 is controlled by capacitor

C3.

Overload protection is provided by sense resistors R18, R19 and R20 through filter R5 and C6 to control input

(pin 5) of chip, U1.

The primary dc voltage (PRDC 1) across C11 is converted to a regulated ac voltage, with the aid of U2 and U3

devices that alternately control switching transistors Q5 and Q6, thereby providing power to the primary winding

of transformer T1. Protection against accidental shorts is provided by sensing resistors R28, R29 and R30,

through filter R27 and C12, to control pin 4 of U2.

The secondary winding of transformer T1, on terminals 6, 7 and 10 provides:

• +12 Vdc thru full wave rectifier D17 and D18 and auctioneering diode D21 (to termi-

nal J2/28A, 28C)

• -12 Vdc thru full wave rectifier D15 and D11 and auctioneering diode D14 (to terminal

J2/30A, 30C)

• +24 Vdc thru voltage doubler circuit C16, C19, D23, C18 and auctioneering diode

D24 (to terminal J7/8A, 8C)

• -24 Vdc thru voltage doubler circuit C17, D20, D25, C19 and auctioneering diode

D22 (to terminal J7/6A, 6C)