AND

a

b

b>a

Selected voltage

PickupVolt_UV1

Operation_UV1=On

BLKUV1

Inverse time

selected

en05000752_ansi.vsd

Inverse

0-DEF

DEF time

selected

OR

PU_UV1

TRUV1

AND

BLKTRUV1

0

ANSI05000752 V1 EN

Figure 298:

Simplified internal logic diagram for built-in first undervoltage step UV1 (step UV2 has the same

internal logic)

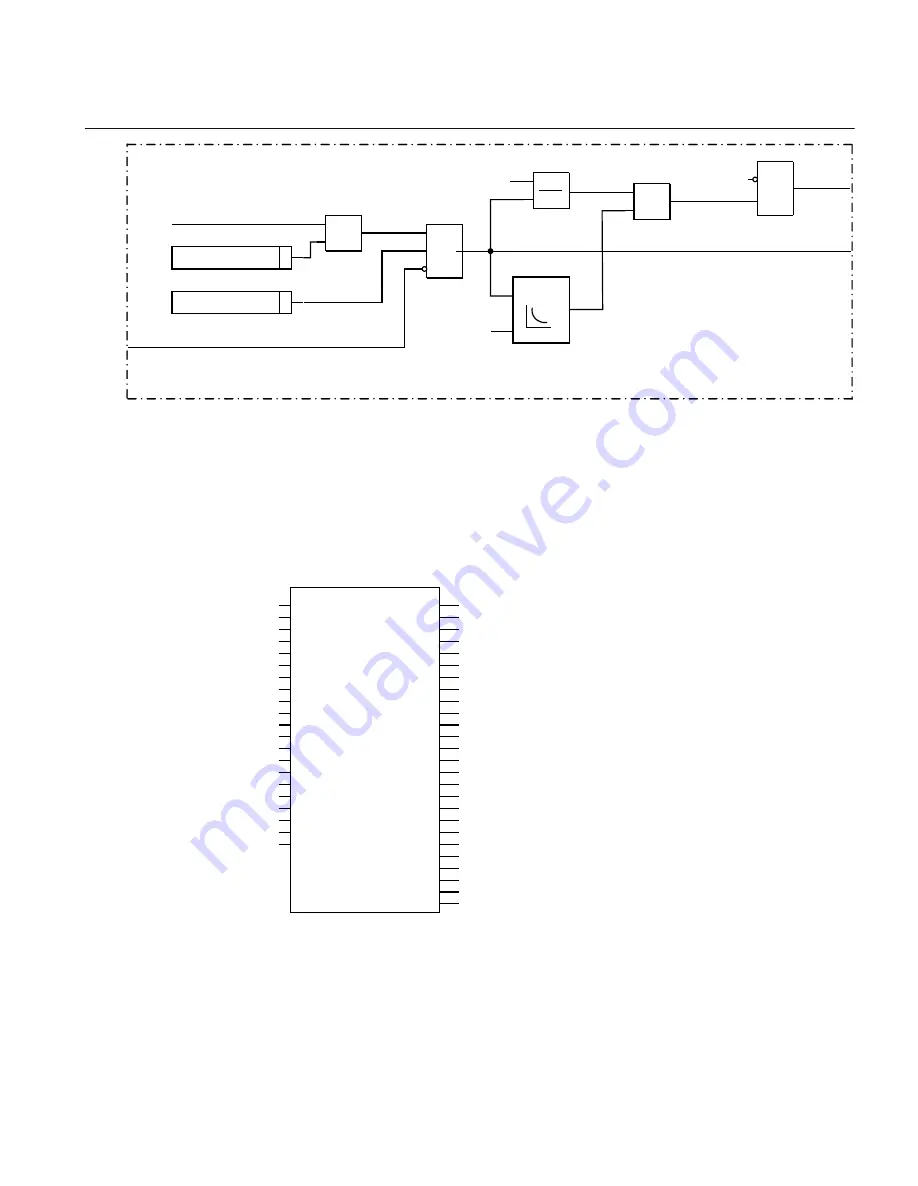

10.1.3

Function block

ANSI05000372-2-en.vsd

CVGAPC

I3P*

V3P*

BLOCK

BLKOC1

BLKOC1TR

ENMLTOC1

BLKOC2

BLKOC2TR

ENMLTOC2

BLKUC1

BLKUC1TR

BLKUC2

BLKUC2TR

BLKOV1

BLKOV1TR

BLKOV2

BLKOV2TR

BLKUV1

BLKUV1TR

BLKUV2

BLKUV2TR

TRIP

TROC1

TROC2

TRUC1

TRUC2

TROV1

TROV2

TRUV1

TRUV2

PICKUP

PU_OC1

PU_OC2

PU_UC1

PU_UC2

PU_OV1

PU_OV2

PU_UV1

PU_UV2

BLK2ND

DIROC1

DIROC2

VDIRLOW

CURRENT

ICOSFI

VOLTAGE

VIANGLE

ANSI05000372 V2 EN

Figure 299:

CVGAPC function block

1MRK505222-UUS C

Section 10

Multipurpose protection

583

Technical reference manual

Summary of Contents for Relion 670 series

Page 1: ...Relion 670 series Line differential protection RED670 ANSI Technical reference manual...

Page 2: ......

Page 40: ...34...

Page 50: ...44...

Page 60: ...54...

Page 126: ...120...

Page 384: ...378...

Page 496: ...490...

Page 556: ...550...

Page 602: ...596...

Page 620: ...614...

Page 794: ...788...

Page 864: ...858...

Page 988: ...982...

Page 998: ...992...

Page 1084: ...1078...

Page 1164: ...1158...

Page 1168: ...1162...

Page 1220: ...1214...

Page 1230: ...1224...

Page 1231: ...1225...