38

Logic function blocks

&KDSWHU

&RPPRQIXQFWLRQV

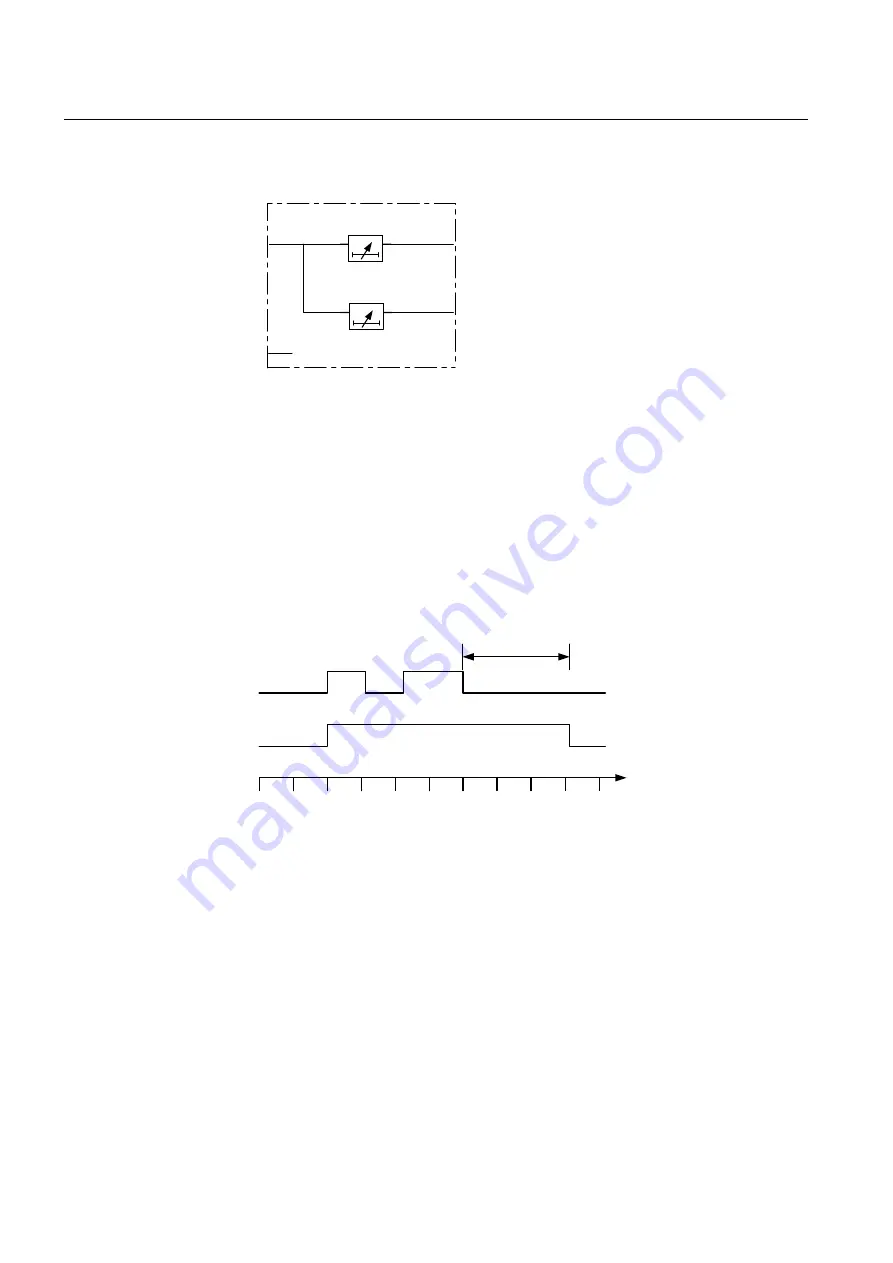

)LJXUH )XQFWLRQEORFNGLDJUDPRIWKH7LPHU/RQJIXQFWLRQ

The input variable to INPUT is obtained delayed a settable time T at output OFF when

the input variable changes from 1 to 0 in accordance with the time pulse diagram, figure

12. The output OFF signal is set to 1 immediately when the input variable changes from

0 to 1.

)LJXUH ([DPSOHRIWLPHGLDJUDPIRUDWLPHUGHOD\HGRQGURSRXWZLWKSUHVHWWLPH

7 V

xx00000526.vsd

OFF

INPUT

ON

T

Time delay 0.0-90000.0s

TLnn

t

t

xx00000528.vsd

INPUT

OFF

T=3s

1

0

1

0

0

1

1

2

3

4

5

6

7

8

9

10

Summary of Contents for REO 517

Page 10: ... RQWHQWV ...

Page 16: ...6 Introduction to the application manual KDSWHU QWURGXFWLRQ ...

Page 64: ...54 Blocking of signals during test KDSWHU RPPRQ IXQFWLRQV ...

Page 88: ...78 Scheme communication logic ZCOM KDSWHU LQH LPSHGDQFH ...

Page 146: ...136 Unbalance protection for capacitor banks TOCC KDSWHU XUUHQW ...

Page 166: ...156 Dead line detection DLD KDSWHU 3RZHU V VWHP VXSHUYLVLRQ ...

Page 378: ...368 Monitoring of DC analog measurements KDSWHU 0RQLWRULQJ ...

Page 384: ...374 Pulse counter logic PC KDSWHU 0HWHULQJ ...

Page 412: ...402 Serial communication modules SCM KDSWHU DWD FRPPXQLFDWLRQ ...

Page 440: ...430 LED indication module KDSWHU DUGZDUH PRGXOHV ...