Appendix B

B-8

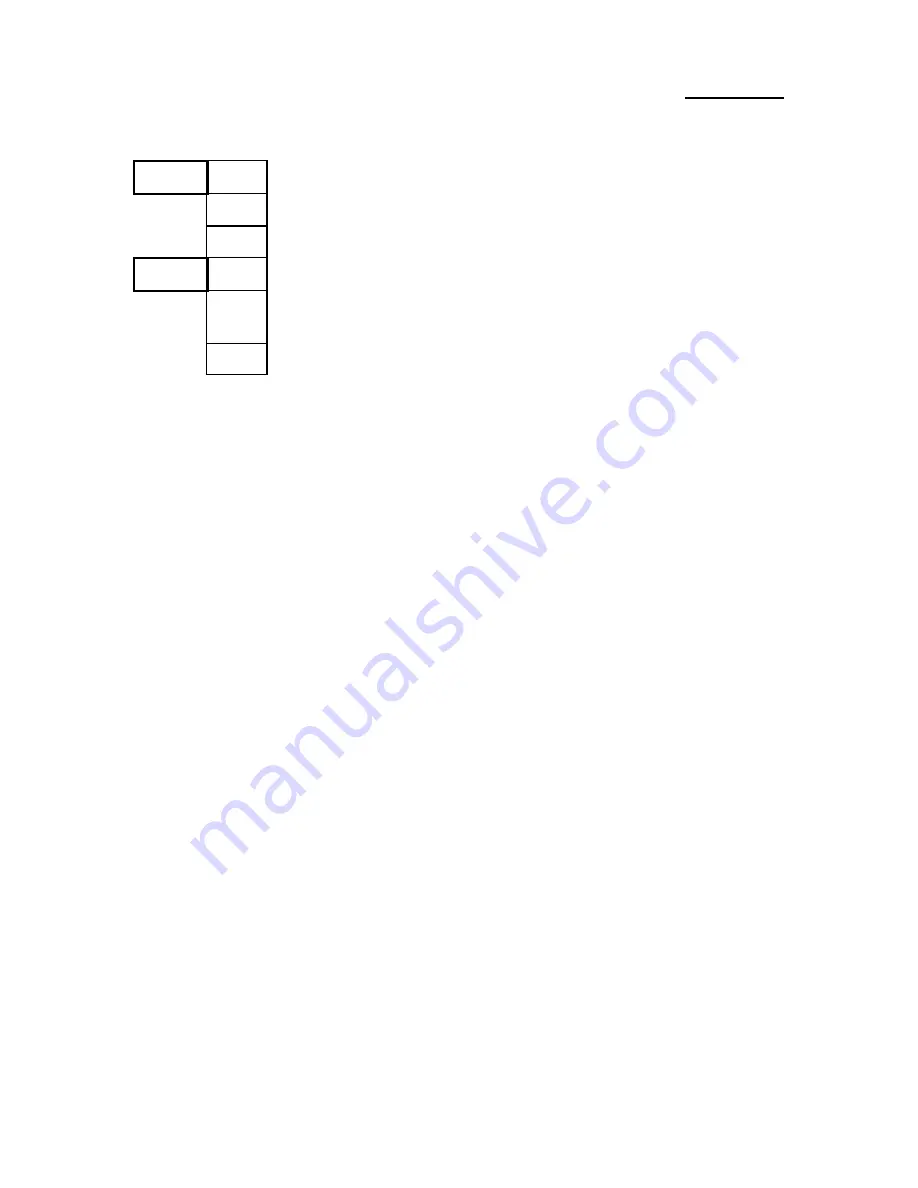

Y

Bus Factor

Power STD

3.15V~3.465V (Recommended voltage is 3.38V)

VR

3.300V~3.465V (Recommended voltage is 3.38V)

VRE

3.450V~3.6V (Recommended voltage is 3.52V)

Timing STD

Standard Timing

MD

Min. Delay (denoting shorter minimum valid delay AC timing

for some signal)

Kit

Supports timing for C55/C88 cache chipsets & design

P54C

1. Beginning with the P54C E-Step, standard timings have been replaced by existing

Min Delay timing

.

P54CS

1. P54CS PPGA UP:No DP,No APIC,No FRC

2. Beginning with the P54C E-Step, standard timings have been replaced by existing

Min Delay timing.

P55C

1. P55C A-Step is NOT production stepping

2. A-1 step:

Vcc and timing on initial samples is 2.9V +/- 0.1V

3. A-2 Step and B step: Vcc and timing on production stepping is 2.8V +/- 0.1V

Summary of Contents for PX5

Page 6: ...1 4 Chapter 1 Layout diagram Fig 1 1 Layout diagram ...

Page 8: ...1 6 Chapter 1 ...

Page 15: ...Installing the Mainboard 2 7 ...

Page 26: ......

Page 63: ...Quick Installation A 7 ...

Page 64: ......

Page 74: ...Appendix C C 2 ...

Page 76: ...Appendix D D 2 ...