147

/

246

ABOV Semiconductor

UART

Un.BFR

Baud rate Fraction Counter Register

9.3.9

Baud rate Fraction Counter Register is 8-bit register.

U0.BFR=0x4000_8024, U1.BFR=0x4000_8124

7

6

5

4

3

2

1

0

BFR

0x00

RW

7

0

BFR

Fractions counter value.

0

Fraction counter is disabled

N

Fraction counter enabled. Fraction compensation mode is

operating. Fraction counter is incremented by FCNT.

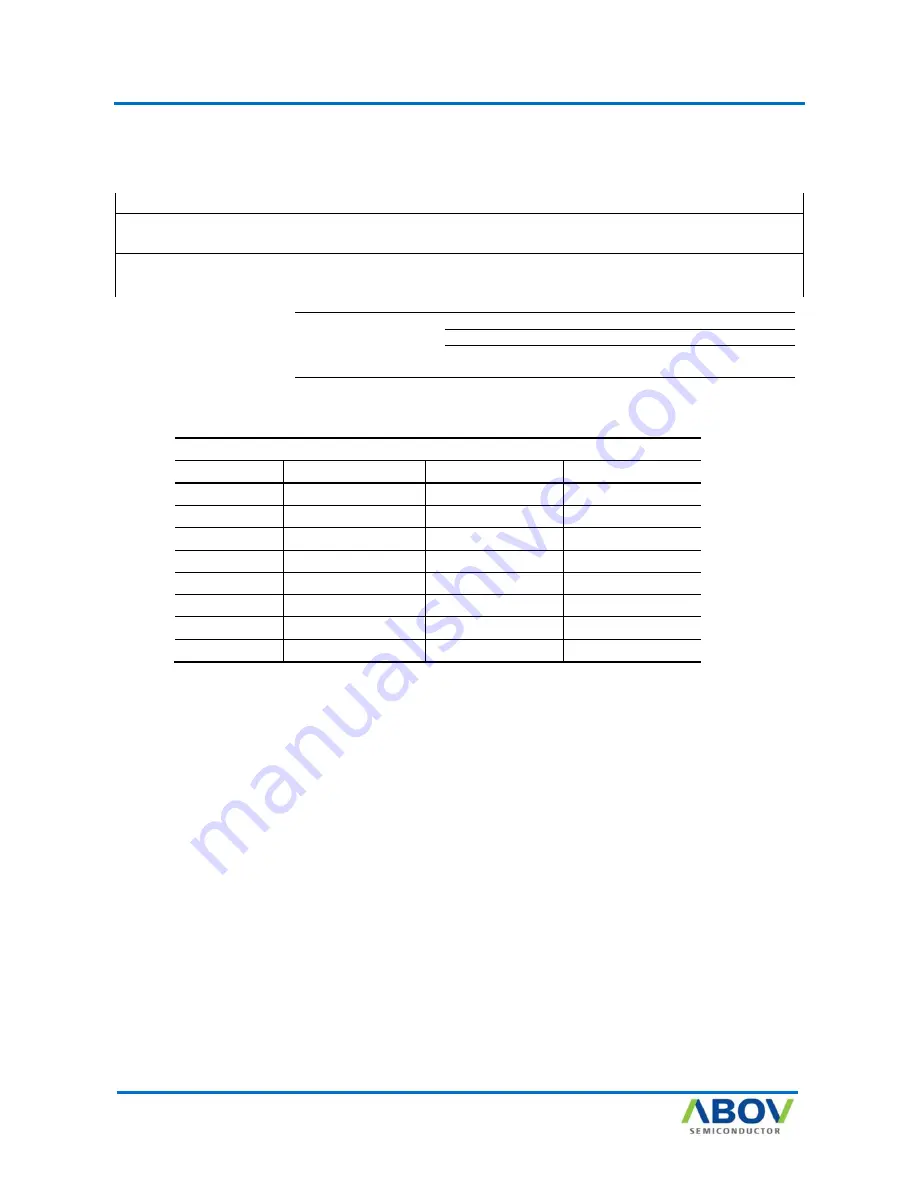

Table9.7. Example of baud rate calculation

UART

clock

=40 MHz

Baud rate

Divider

FCNT

Error (%)

1200

2083

85

0.00%

2400

1041

170

0.00%

4800

520

213

0.00%

9600

260

106

0.00%

19200

130

53

0.00%

38400

65

262

0.00%

57600

43

103

0.00%

115200

21

179

0.01%

FCNT = Float ∗ 256

FCNT value can calculated above equation. For example, the target baud rate is 4800 bps and UART

clock

is 40MHz case,

the BDR value is 520.8333. The integer number 520 should be the BDR value and the floating number 0.8333 will make

the FNCT value as below.

FCNT = 0.8333 * 256 = 213.3333, so the FCNT value is 213.

8-bit fractional counter will count up by FCNT value every (baud rate)/16 periods and whenever fractional counter

overflow is happen, the divisor value will increment by 1. So this period will be compensated. Then next period, the

divisor value will return to original set value.

Summary of Contents for AC30M1x64

Page 3: ...3 246 ABOV Semiconductor INTRODUCTION SECTION 1 INTRODUCTION...

Page 4: ...4 246 4 246 AC30M1x64 1x32 ABOV Semiconductor OVERVIEW CHAPTER 1...

Page 18: ...18 246 18 246 ABOV Semiconductor AC30M1x64 1x32 CPU CHAPTER 2...

Page 22: ...22 246 22 246 ABOV Semiconductor AC30M1x64 1x32 Boot Mode CHAPTER 3...

Page 26: ...26 246 26 246 ABOV Semiconductor AC30M1x64 1x32 SECTION 2 PERIPHERALS...

Page 27: ...27 246 ABOV Semiconductor System Control Unit SCU SYSTEM CONTROL UNIT SCU CHAPTER 1...

Page 69: ...69 246 ABOV Semiconductor Port Control Unit PCU PORT CONTROL UNIT PCU CHAPTER 2...

Page 85: ...85 246 ABOV Semiconductor General Purpose I O GPIO GENERAL PURPOSE I O GPIO CHAPTER 3...

Page 92: ...92 246 92 246 AC30M1x64 1x32 ABOV Semiconductor FLASH MEMORY CONTROLLER CHAPTER 4...

Page 105: ...105 246 ABOV Semiconductor Internal SRAM INTERNAL SRAM CHAPTER 5...

Page 107: ...107 246 ABOV Semiconductor Watch Dog Timer WATCH DOG TIMER WDT CHAPTER 6...

Page 113: ...113 246 ABOV Semiconductor 16 bit Timer 16 BIT TIMER CHAPTER 7...

Page 129: ...129 246 ABOV Semiconductor FRT FREE RUN TIMER FRT CHAPTER 8...

Page 134: ...134 246 134 246 ABOV Semiconductor AC30M1x64 1x32 FUNCTION DESCRIPTION 8 3...

Page 135: ...135 246 UART ABOV Semiconductor UNIVERSAL ASYNCHRONOUS CHAPTER 9 RECEIVER TRANSMITTER UART...

Page 151: ...151 246 ABOV Semiconductor UART Figure 9 6 Transmit interrupt timing diagram...

Page 152: ...152 246 152 246 ABOV Semiconductor AC30M1x64 1x32 SERIAL PERIPHERAL INTERFACE SPI CHAPTER 10...

Page 164: ...164 246 164 246 ABOV Semiconductor AC30M1x64 1x32 I2 C Interface CHAPTER 11...

Page 185: ...185 246 ABOV Semiconductor Motor PWM MOTOR PULSE WIDTH MODULATOR CHAPTER 12 MPWM...

Page 215: ...215 246 ABOV Semiconductor Divider DIVIDER DIV64 CHAPTER 13...

Page 221: ...221 246 ABOV Semiconductor 12 BIT A D Converter 12BIT A D CONVERTER CHAPTER 14...

Page 235: ...235 246 ABOV Semiconductor CHARACTERISTIC SECTION 3 CHARACTERISTIC...

Page 236: ...236 246 236 246 ABOV Semiconductor AC30M1x64 1x32 Electrical Characteristic CHAPTER 1...

Page 243: ...243 246 ABOV Semiconductor Package Package CHAPTER 2...