180 / 246

180 / 246

ABOV Semiconductor

AC30M1x64/1x32

Arbitration

11.4.6

A master may start a transfer only if the bus is free. Two or more masters may generate a START condition within the

minimum hold time of the START condition which results in a defined START condition to the bus.

Arbitration takes place on the SDA line, while the SCL line is at the “H” level, in such a way that the master which

transmits “H” level, while another master is transmitting “L” level will switch off its DATA output stage because the level

on the bus doesn’t correspond to its own level.

Arbitration can continue for many bits. Its first stage is comparison of the address bits. If the masters are each trying to

address the same device, arbitration continues with comparison of the data-bits if they are master-transmitter or

acknowledge-bits if they are master-receiver. Because address and data information on the I

2

C-bus is determined by the

winning master, no information is lost during the arbitration process.

A master that loses the arbitration can generate clock pulses until the end of the byte in which it loses the arbitration.

If a master also incorporates a slave function and it loses arbitration during the addressing stage, it’s possible that the

winning master is trying to address it. The losing master must therefore switch over immediately to its slave mode.

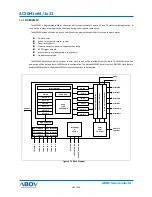

Figure 11.11 shows the arbitration procedure for two masters. Of course, more may be involved (depending on how

many masters are connected to the bus). The moment there is a difference between the internal data level of the master

generating Device1 Data out and the actual level on the SDA line, its data output is switched off, which means that a “H”

output level is then connected to the bus. This will not affect the data transfer initiated by the winning master.

Figure 11.11 Arbitration procedure between two masters

Device1

DataOut

SCL on BUS

Device2

DataOut

SDA on BUS

S

Arbitration Process not adapted

Device 1 loses Arbitration

Device1 outputs High

Summary of Contents for AC30M1x64

Page 3: ...3 246 ABOV Semiconductor INTRODUCTION SECTION 1 INTRODUCTION...

Page 4: ...4 246 4 246 AC30M1x64 1x32 ABOV Semiconductor OVERVIEW CHAPTER 1...

Page 18: ...18 246 18 246 ABOV Semiconductor AC30M1x64 1x32 CPU CHAPTER 2...

Page 22: ...22 246 22 246 ABOV Semiconductor AC30M1x64 1x32 Boot Mode CHAPTER 3...

Page 26: ...26 246 26 246 ABOV Semiconductor AC30M1x64 1x32 SECTION 2 PERIPHERALS...

Page 27: ...27 246 ABOV Semiconductor System Control Unit SCU SYSTEM CONTROL UNIT SCU CHAPTER 1...

Page 69: ...69 246 ABOV Semiconductor Port Control Unit PCU PORT CONTROL UNIT PCU CHAPTER 2...

Page 85: ...85 246 ABOV Semiconductor General Purpose I O GPIO GENERAL PURPOSE I O GPIO CHAPTER 3...

Page 92: ...92 246 92 246 AC30M1x64 1x32 ABOV Semiconductor FLASH MEMORY CONTROLLER CHAPTER 4...

Page 105: ...105 246 ABOV Semiconductor Internal SRAM INTERNAL SRAM CHAPTER 5...

Page 107: ...107 246 ABOV Semiconductor Watch Dog Timer WATCH DOG TIMER WDT CHAPTER 6...

Page 113: ...113 246 ABOV Semiconductor 16 bit Timer 16 BIT TIMER CHAPTER 7...

Page 129: ...129 246 ABOV Semiconductor FRT FREE RUN TIMER FRT CHAPTER 8...

Page 134: ...134 246 134 246 ABOV Semiconductor AC30M1x64 1x32 FUNCTION DESCRIPTION 8 3...

Page 135: ...135 246 UART ABOV Semiconductor UNIVERSAL ASYNCHRONOUS CHAPTER 9 RECEIVER TRANSMITTER UART...

Page 151: ...151 246 ABOV Semiconductor UART Figure 9 6 Transmit interrupt timing diagram...

Page 152: ...152 246 152 246 ABOV Semiconductor AC30M1x64 1x32 SERIAL PERIPHERAL INTERFACE SPI CHAPTER 10...

Page 164: ...164 246 164 246 ABOV Semiconductor AC30M1x64 1x32 I2 C Interface CHAPTER 11...

Page 185: ...185 246 ABOV Semiconductor Motor PWM MOTOR PULSE WIDTH MODULATOR CHAPTER 12 MPWM...

Page 215: ...215 246 ABOV Semiconductor Divider DIVIDER DIV64 CHAPTER 13...

Page 221: ...221 246 ABOV Semiconductor 12 BIT A D Converter 12BIT A D CONVERTER CHAPTER 14...

Page 235: ...235 246 ABOV Semiconductor CHARACTERISTIC SECTION 3 CHARACTERISTIC...

Page 236: ...236 246 236 246 ABOV Semiconductor AC30M1x64 1x32 Electrical Characteristic CHAPTER 1...

Page 243: ...243 246 ABOV Semiconductor Package Package CHAPTER 2...