MC95FG0128A

Aug 02, 2018 Ver.2.9

105

1

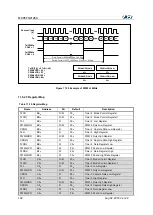

Timer X Output enable

POL

Configure PWM polarity

0

Negative (Duty Match: Clear)

1

Positive (Duty Match: Set)

T2L, T3L, T4L, T5L (Timer 2~5 Low Register, Read Case) : BCH, C4H, CCH,

2F3AH

7

6

5

4

3

2

1

0

TxL7

TxL6

TxL5

TxL4

TxL3

TxL2

TxL1

TxL0

R

R

R

R

R

R

R

R

Initial value : 00

H

TxL[7:0]

TxL Counter Period Low data.

CDR2L, CDR3L, CDR4L, CDR5L (Capture 2~5 Data Low Register, Read Case) :

BCH, C4H, CCH, 2F3AH

7

6

5

4

3

2

1

0

CDRxL07

CDRxL06

CDRxL05

CDRxL04

CDRxL03

CDRxL02

CDRxL01

CDRxL00

R

R

R

R

R

R

R

R

Initial value : 00

H

CDRxL[7:0]

Tx Capture Low data.

PWM2LDR, PWM3LDR, PWM4LDR, PWM5LDR (PWM 2~5 Low Duty Register,

Write Case) : BCH, C4H, CCH, 2F3AH

7

6

5

4

3

2

1

0

PWMxLD7

PWMxLD6

PWMxLD5

PWMxLD4

PWMxLD3

PWMxLD2

PWMxLD1

PWMxLD0

W

W

W

W

W

W

W

W

Initial value : 00

H

PWMxLD[7:0]

Tx PWM Duty Low data

Note) only write, when PWMxE

‘1’

T2H, T3H, T4H, T5H (Timer 2~5 High Register, Read Case) : BDH, C5H, CDH,

2F3BH

7

6

5

4

3

2

1

0

TxH7

TxH6

TxH5

TxH4

TxH3

TxH2

TxH1

TxH0

R

R

R

R

R

R

R

R

Initial value : 00

H

TxH[7:0]

TxH Counter Period High data.

CDR2H, CDR3H, CDR4H, CDR5H (Capture 2~5 Data High Register, Read Case) :

BDH, C5H, CDH, 2F3BH

7

6

5

4

3

2

1

0

CDRxH07

CDRxH06

CDRxH05

CDRxH04

CDRxH03

CDRxH02

CDRxH01

CDRxH00

R

R

R

R

R

R

R

R

Initial value : 00

H

Summary of Contents for MC95FG0128A

Page 26: ...MC95FG0128A 26 Aug 02 2018 Ver 2 9 4 Package Diagram Figure 4 1 100 pin LQFP package...

Page 27: ...MC95FG0128A Aug 02 2018 Ver 2 9 27 Figure 4 2 80 pin LQFP package...

Page 28: ...MC95FG0128A 28 Aug 02 2018 Ver 2 9 Figure 4 3 80 pin MQFP package...

Page 29: ...MC95FG0128A Aug 02 2018 Ver 2 9 29 Figure 4 4 64 pin LQFP package...

Page 30: ...MC95FG0128A 30 Aug 02 2018 Ver 2 9 Figure 4 5 64 pin LQFP14 package...