MC95FG0128A

Aug 02, 2018 Ver.2.9

81

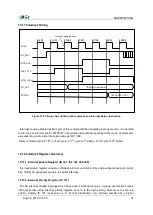

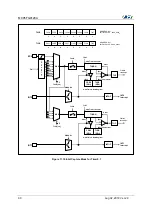

11.3.4 Watch Dog Timer Register description

The Watch dog timer (WDT) Register consists of Watch Dog Timer Register (WDTR), Watch Dog

Timer Counter Register (WDTCR) and Watch Dog Timer Mode Register (WDTMR).

11.3.5 Register description for Watch Dog Timer

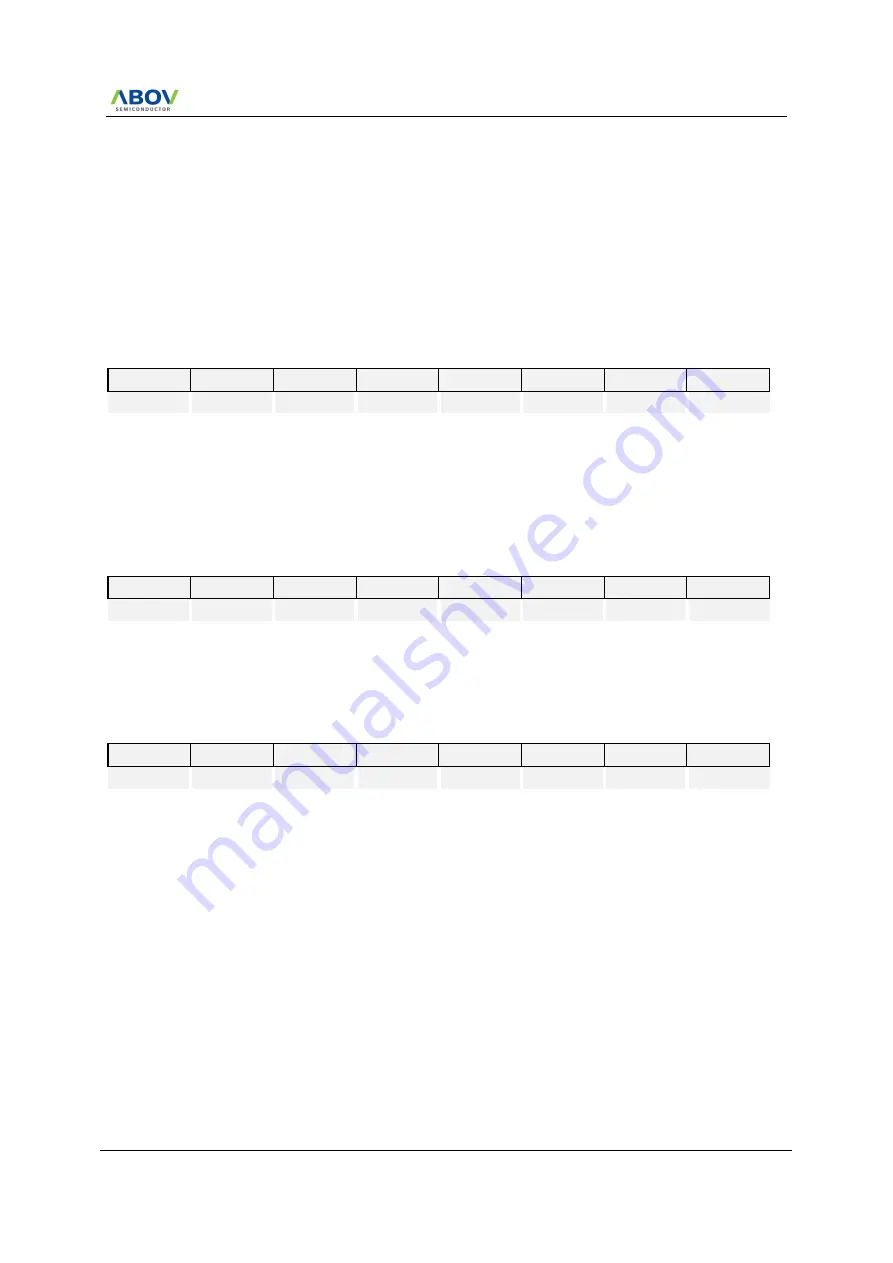

WDTR (Watch Dog Timer Register: Write Case) : 8EH

7

6

5

4

3

2

1

0

WDTR7

WDTR6

WDTR5

WDTR4

WDTR3

WDTR2

WDTR1

WDTR0

W

W

W

W

W

W

W

W

Initial value : FFH

WDTR[7:0]

Set a period

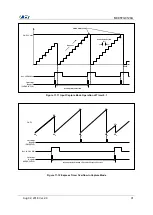

WDT Interrupt Interval=(BIT Interrupt Interval) x(WDTR Value+1)

Note) To guarantee proper operation, the data should be greater than 01H.

WDTCR (Watch Dog Timer Counter Register: Read Case) : 8EH

7

6

5

4

3

2

1

0

WDTCR7

WDTCR6

WDTCR5

WDTCR4

WDTCR3

WDTCR2

WDTCR1

WDTCR0

R

R

R

R

R

R

R

R

Initial value : 00H

WDTCR[7:0]

WDT Counter

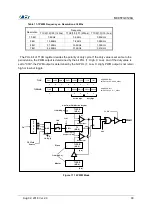

WDTMR (Watch Dog Timer Mode Register) : 8DH

7

6

5

4

3

2

1

0

WDTEN

WDTRSON

WDTCL

-

-

-

-

WDTIFR

R/W

R/W

R/W

-

-

-

-

R/W

Initial value : 00H

WDTEN

Control WDT operation

0

disable

1

enable

WDTRSON

Control WDT Reset operation

0

Free Running 8-bit timer

1

Watch Dog Timer Reset ON

WDTCL

Clear WDT Counter

0

Free Run

1

Clear WDT Counter (auto clear after 1 Cycle)

WDTIFR

When WDT Interrupt occurs, this bit becomes

‘1’. For clearing bit, write

‘0’ to this bit or auto clear by INT_ACK signal.

0

WDT Interrupt no generation

1

WDT Interrupt generation

Summary of Contents for MC95FG0128A

Page 26: ...MC95FG0128A 26 Aug 02 2018 Ver 2 9 4 Package Diagram Figure 4 1 100 pin LQFP package...

Page 27: ...MC95FG0128A Aug 02 2018 Ver 2 9 27 Figure 4 2 80 pin LQFP package...

Page 28: ...MC95FG0128A 28 Aug 02 2018 Ver 2 9 Figure 4 3 80 pin MQFP package...

Page 29: ...MC95FG0128A Aug 02 2018 Ver 2 9 29 Figure 4 4 64 pin LQFP package...

Page 30: ...MC95FG0128A 30 Aug 02 2018 Ver 2 9 Figure 4 5 64 pin LQFP14 package...