MC96F6432

116

June 22, 2018 Ver. 2.9

11.3 Watch Dog Timer

11.3.1 Overview

The watchdog timer rapidly detects the CPU malfunction such as endless looping caused by noise or something

like that, and resumes the CPU to the normal state. The watchdog timer signal for malfunction detection can be

used as either a CPU reset or an interrupt request. When the watchdog timer is not being used for malfunction

detection, it can be used as a timer to generate an interrupt at fixed intervals. It is possible to use free running 8-

bit timer mode (WDTRSON=

’0’) or watch dog timer mode (WDTRSON=’1’) as setting WDTCR[6] bit. If WDTCR[5]

is written to

‘1’, WDT counter value is cleared and counts up. After 1 machine cycle, this bit is cleared to ‘0’

automatically. The watchdog timer consists of 8-bit binary counter and the watchdog timer data register. When

the value of 8-bit binary counter is equal to the 8 bits of WDTCNT, the interrupt request flag is generated. This

can be used as Watchdog timer interrupt or reset of CPU in accordance with the bit WDTRSON.

The input clock source of watch dog timer is the BIT overflow. The interval of watchdog timer interrupt is decided

by BIT overflow period and WDTDR set value. The equation can be described as

WDT Interrupt Interval = (BIT Interrupt Interval) X (WDTDR Value+1)

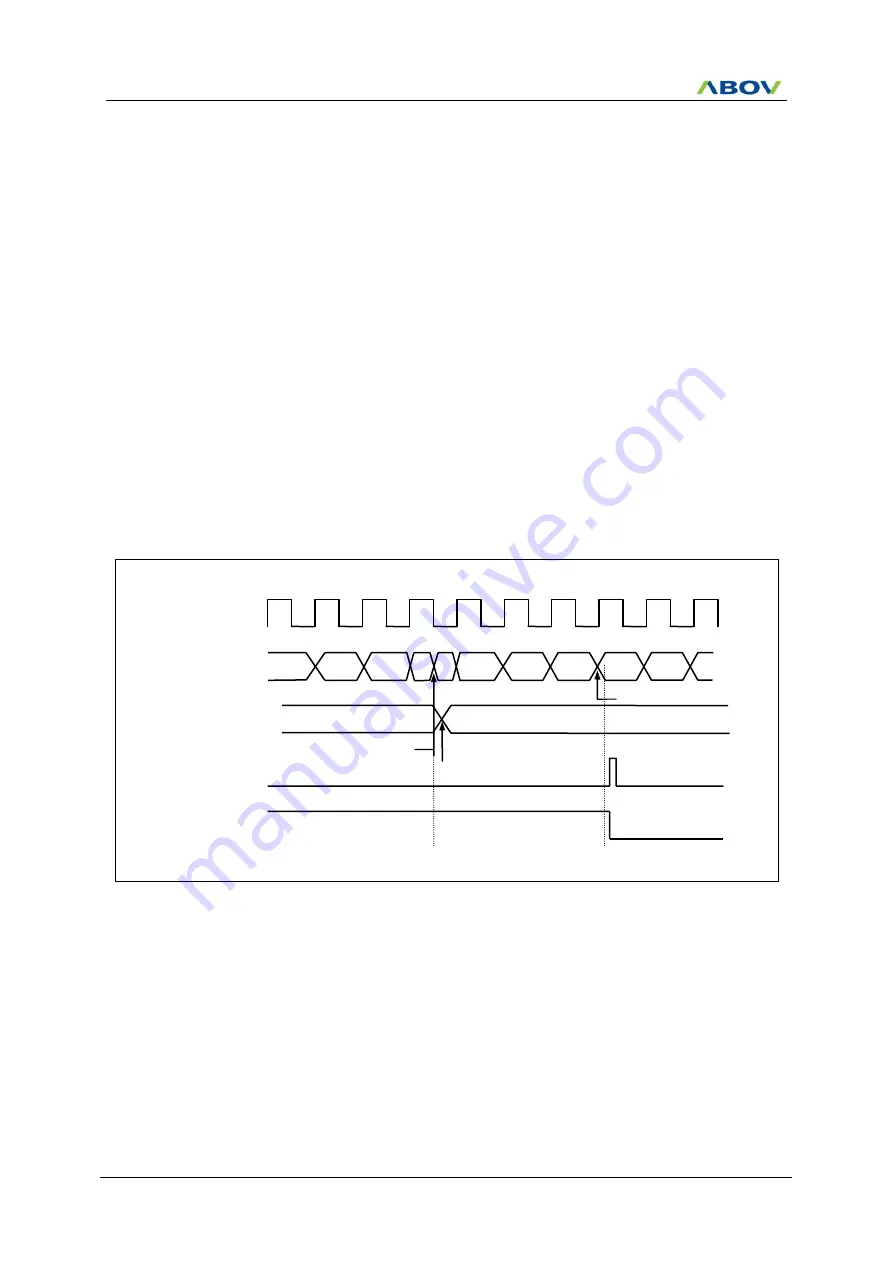

11.3.2 WDT Interrupt Timing Waveform

Figure 11.3 Watch Dog Timer Interrupt Timing Waveform

Source Clock

BIT Overflow

WDTCNT[7:0]

WDTDR[7:0]

WDTIFR

Interrupt

WDTRESETB

WDTCL

Occur

WDTDR

0000_0011b

Match

Detect

Counter Clear

RESET

0

1

2

3

0

1

2

3

0

1

2

n

3

Summary of Contents for MC96F6432 Series

Page 24: ...MC96F6432 24 June 22 2018 Ver 2 9 4 Package Diagram Figure 4 1 48 Pin LQFP 0707 Package...

Page 25: ...MC96F6432 June 22 2018 Ver 2 9 25 Figure 4 2 44 Pin MQFP Package...

Page 26: ...MC96F6432 26 June 22 2018 Ver 2 9 Figure 4 3 32 Pin LQFP Package...

Page 27: ...MC96F6432 June 22 2018 Ver 2 9 27 Figure 4 4 32 Pin SOP Package...

Page 28: ...MC96F6432 28 June 22 2018 Ver 2 9 Figure 4 5 28 Pin SOP Package...