MC96F6432

June 22, 2018 Ver. 2.9

141

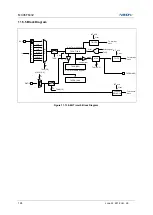

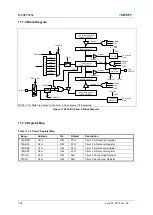

11.7 Timer 2

11.7.1 Overview

The 16-bit timer 2 consists of multiplexer, timer 2 A data high/low register, timer 2 B data high/low register and

timer 2 control high/low register (T2ADRH, T2ADRL, T2BDRH, T2BDRL, T2CRH, T2CRL).

It has four operating modes:

-

16-bit timer/counter mode

-

16-bit capture mode

-

16-bit PPG output mode (one-shot mode)

-

16-bit PPG output mode (repeat mode)

The timer/counter 2 can be divided clock of the system clock selected from prescaler output and T1 A Match

(timer 1 A match signal). The clock source is selected by clock selection logic which is controlled by the clock

selection bits (T2CK[2:0]).

- TIMER 2 clock source: f

X

/1, 2, 4, 8, 32, 128, 512 and T1 A Match

In the capture mode, by EINT12, the data is captured into input capture data register (T2BDRH/T2BDRL). In

timer/counter mode, whenever counter value is equal to T2ADRH/L, T2O port toggles. Also the timer 2 outputs

PWM wave form to PWM2O port in the PPG mode.

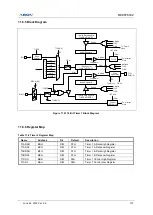

Table 11-9 Timer 2 Operating Modes

T2EN

P1FSRL[3:2]

T2MS[1:0]

T2CK[2:0]

Timer 2

1

11

00

XXX

16 Bit Timer/Counter Mode

1

00

01

XXX

16 Bit Capture Mode

1

11

10

XXX

16 Bit PPG Mode

(one-shot mode)

1

11

11

XXX

16 Bit PPG Mode

(repeat mode)

Summary of Contents for MC96F6432 Series

Page 24: ...MC96F6432 24 June 22 2018 Ver 2 9 4 Package Diagram Figure 4 1 48 Pin LQFP 0707 Package...

Page 25: ...MC96F6432 June 22 2018 Ver 2 9 25 Figure 4 2 44 Pin MQFP Package...

Page 26: ...MC96F6432 26 June 22 2018 Ver 2 9 Figure 4 3 32 Pin LQFP Package...

Page 27: ...MC96F6432 June 22 2018 Ver 2 9 27 Figure 4 4 32 Pin SOP Package...

Page 28: ...MC96F6432 28 June 22 2018 Ver 2 9 Figure 4 5 28 Pin SOP Package...