MC96F6432

June 22, 2018 Ver. 2.9

159

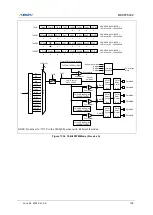

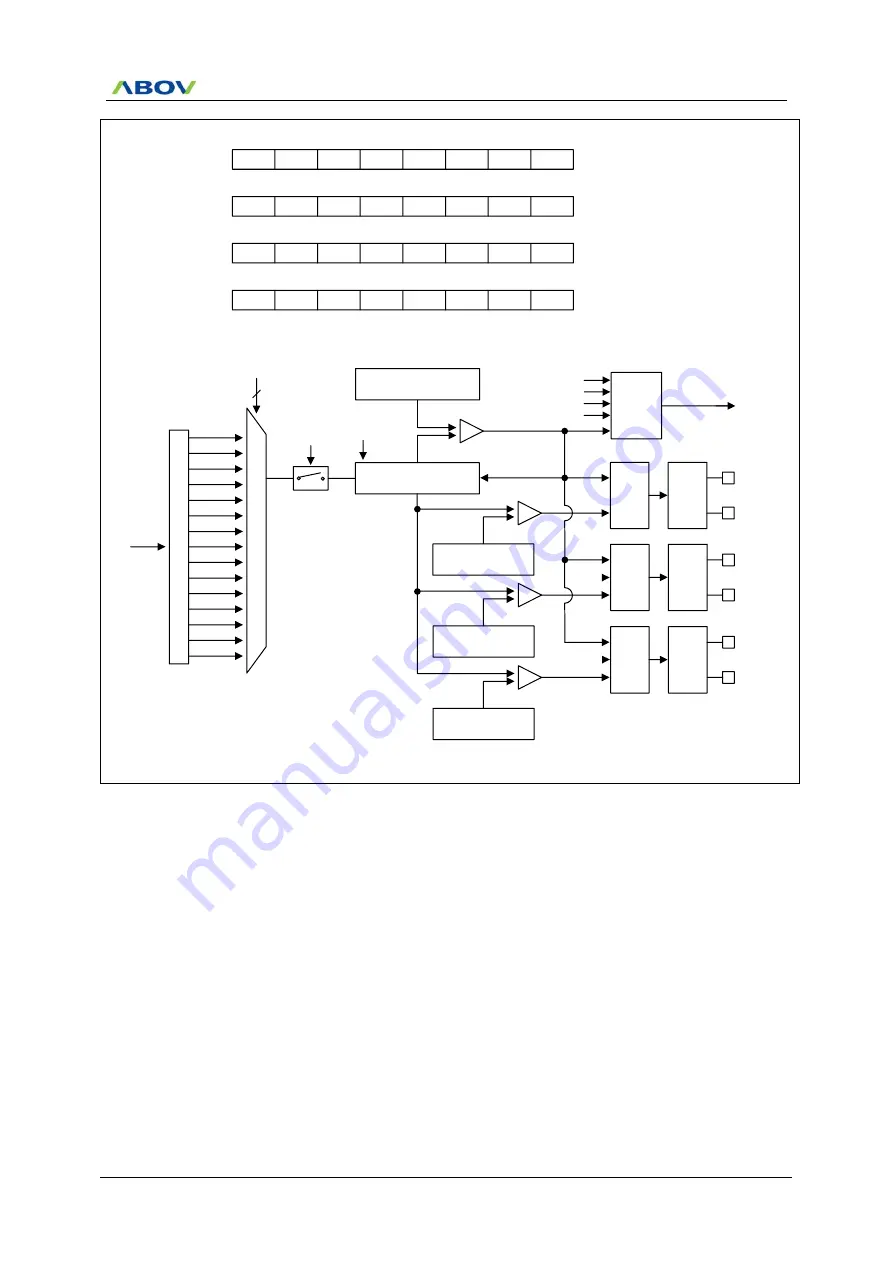

P

r

e

s

c

a

l

e

r

fx

M

U

X

fx/2

fx/4

fx/16

fx/32

fx/64

fx/8

fx/1

Comparator

10-bit Counter

2Bit + T4CNT

10-bit A Data Register

T4ADRH/T4ADRL

Control

Up/Down

Comparator

T4PPRH/T4PPRL (10Bit)

Period Match

PWM

Output

Control

A-ch

PWM4AA

T4CN

4

T4CK[3:0]

fx/128

fx/256

fx/1024

fx/2048

fx/4096

fx/512

fx/8192

fx/16384

Timer 4 PWM Period Register

T4ST

PWM

Delay

Control

A-ch

PWM4AB

Comparator

10-bit B Data Register

T4BDRH/T4BDRL

PWM

Output

Control

B-ch

PWM4BA

PWM

Delay

Control

B-ch

PWM4BB

Comparator

10-bit C Data Register

T4CDRH/T4CDRL

PWM

Output

Control

C-ch

PWM4CA

PWM

Delay

Control

C-ch

PWM4CB

A Match

B Match

C Match

Interrupt

Generator

A Match

B Match

C Match

Bottom (Underflow)

To interrupt

block

FORCA

T4PCR2

0

ADDRESS:1004H (ESFR)

INITIAL VALUE : 0000_0000B

–

PAAOE

PABOE

PBAOE

PBBOE

PCAOE

PCBOE

–

X

X

X

X

X

X

HZCLR

T4PCR3

X

ADDRESS:1005H (ESFR)

INITIAL VALUE : 0000_0000B

POLBO

POLAA

POLAB

POLBA

POLBB

POLCA

POLCB

X

X

X

X

X

X

X

16BIT

T4CR

0

ADDRESS:1002H (ESFR)

INITIAL VALUE : 0000_0000B

T4MS

T4CN

T4ST

T4CK3

T4CK2

T4CK1

T4CK0

X

X

X

X

X

X

X

PWM4E

T4PCR1

1

ADDRESS:1003H (ESFR)

INITIAL VALUE : 0000_0000B

ESYNC

BMOD

PHLT

UPDT

UALL

NOPS1

NOPS0

X

X

X

X

X

X

X

NOTE: Do not set to

“1111b” in the T4CK[3:0], when two 8-bit timer 3/4 modes.

Figure 11.34 10-Bit PWM Mode (Force 6-ch)

Summary of Contents for MC96F6432 Series

Page 24: ...MC96F6432 24 June 22 2018 Ver 2 9 4 Package Diagram Figure 4 1 48 Pin LQFP 0707 Package...

Page 25: ...MC96F6432 June 22 2018 Ver 2 9 25 Figure 4 2 44 Pin MQFP Package...

Page 26: ...MC96F6432 26 June 22 2018 Ver 2 9 Figure 4 3 32 Pin LQFP Package...

Page 27: ...MC96F6432 June 22 2018 Ver 2 9 27 Figure 4 4 32 Pin SOP Package...

Page 28: ...MC96F6432 28 June 22 2018 Ver 2 9 Figure 4 5 28 Pin SOP Package...