MC96F6432

June 22, 2018 Ver. 2.9

195

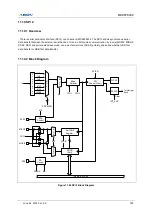

11.12 USI0 (UART + SPI + I2C)

11.12.1 Overview

The USI0 consists of USI0 control register1/2/3/4, USI0 status register 1/2, USI0 baud-rate generation register,

USI0 data register, USI0 SDA hold time register, USI0 SCL high period register, USI0 SCL low period register,

and USI0 slave address register (USI0CR1, USI0CR2, USI0CR3, USI0CR4, USI0ST1, USI0ST2, USI0BD,

USI0DR, USI0SDHR, USI0SCHR, USI0SCLR, USI0SAR).

The operation mode is selected by the operation mode of USI0 selection bits (USI0MS[1:0]).

It has four operating modes:

- Asynchronous mode (UART)

- Synchronous mode

- SPI mode

- I2C mode

Summary of Contents for MC96F6432 Series

Page 24: ...MC96F6432 24 June 22 2018 Ver 2 9 4 Package Diagram Figure 4 1 48 Pin LQFP 0707 Package...

Page 25: ...MC96F6432 June 22 2018 Ver 2 9 25 Figure 4 2 44 Pin MQFP Package...

Page 26: ...MC96F6432 26 June 22 2018 Ver 2 9 Figure 4 3 32 Pin LQFP Package...

Page 27: ...MC96F6432 June 22 2018 Ver 2 9 27 Figure 4 4 32 Pin SOP Package...

Page 28: ...MC96F6432 28 June 22 2018 Ver 2 9 Figure 4 5 28 Pin SOP Package...