MC96F6432

June 22, 2018 Ver. 2.9

197

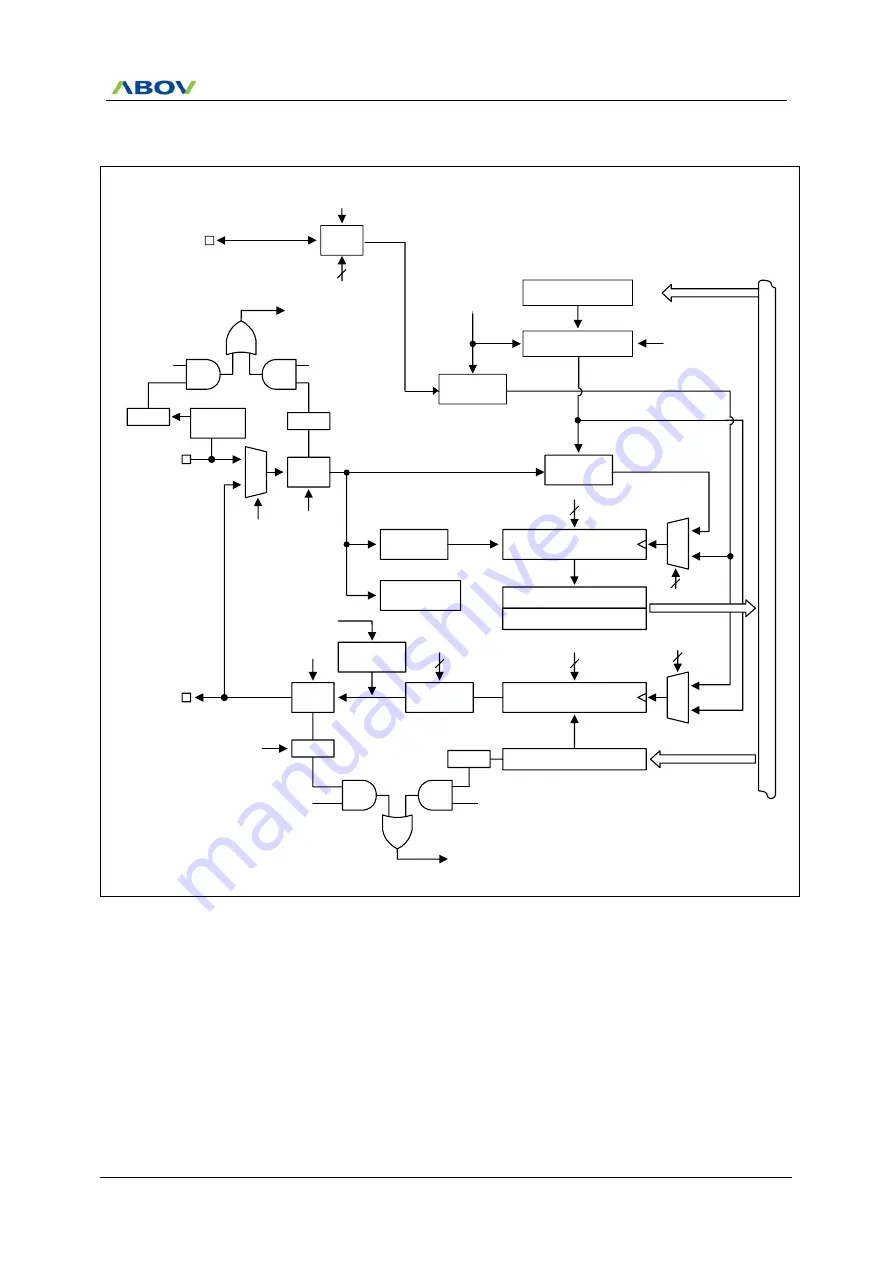

11.12.3 USI0 UART Block Diagram

RXD0

Rx

Control

Clock

Recovery

Receive Shift Register

(RXSR)

Data

Recovery

DOR0/PE0/FE0

Checker

USI0DR[0], USI0RX8[0], (Rx)

USI0DR[1], USI0RX8[1], (Rx)

TXD0

Tx

Control

Stop bit

Generator

Parity

Generator

Transmit Shift Register

(TXSR)

USI0DR, USI0TX8, (Tx)

USI0P[1:0]

M

U

X

LOOPS0

TXC0

TXCIE0

DRIE0

DRE0

Empty signal

To interrupt

block

INT_ACK

Clear

RXC0

RXCIE0

WAKEIE0

WAKE0

At Stop mode

To interrupt

block

SCLK

(fx: System clock)

Low level

detector

2

USI0S[2:0]

3

USI0S[2:0]

3

TXE0

RXE0

DBLS0

USI0SB

Baud Rate Generator

USI0BD

I

N

T

E

R

N

A

L

B

U

S

L

I

N

E

SCK0

ACK

Control

Clock

Sync Logic

Master

USI0MS[1:0]

M

U

X

M

U

X

USI0MS[1:0]

USI0MS[1:0]

2

2

2

Figure 11.57 USI0 UART Block Diagram

Summary of Contents for MC96F6432 Series

Page 24: ...MC96F6432 24 June 22 2018 Ver 2 9 4 Package Diagram Figure 4 1 48 Pin LQFP 0707 Package...

Page 25: ...MC96F6432 June 22 2018 Ver 2 9 25 Figure 4 2 44 Pin MQFP Package...

Page 26: ...MC96F6432 26 June 22 2018 Ver 2 9 Figure 4 3 32 Pin LQFP Package...

Page 27: ...MC96F6432 June 22 2018 Ver 2 9 27 Figure 4 4 32 Pin SOP Package...

Page 28: ...MC96F6432 28 June 22 2018 Ver 2 9 Figure 4 5 28 Pin SOP Package...