MC96F6432

226

June 22, 2018 Ver. 2.9

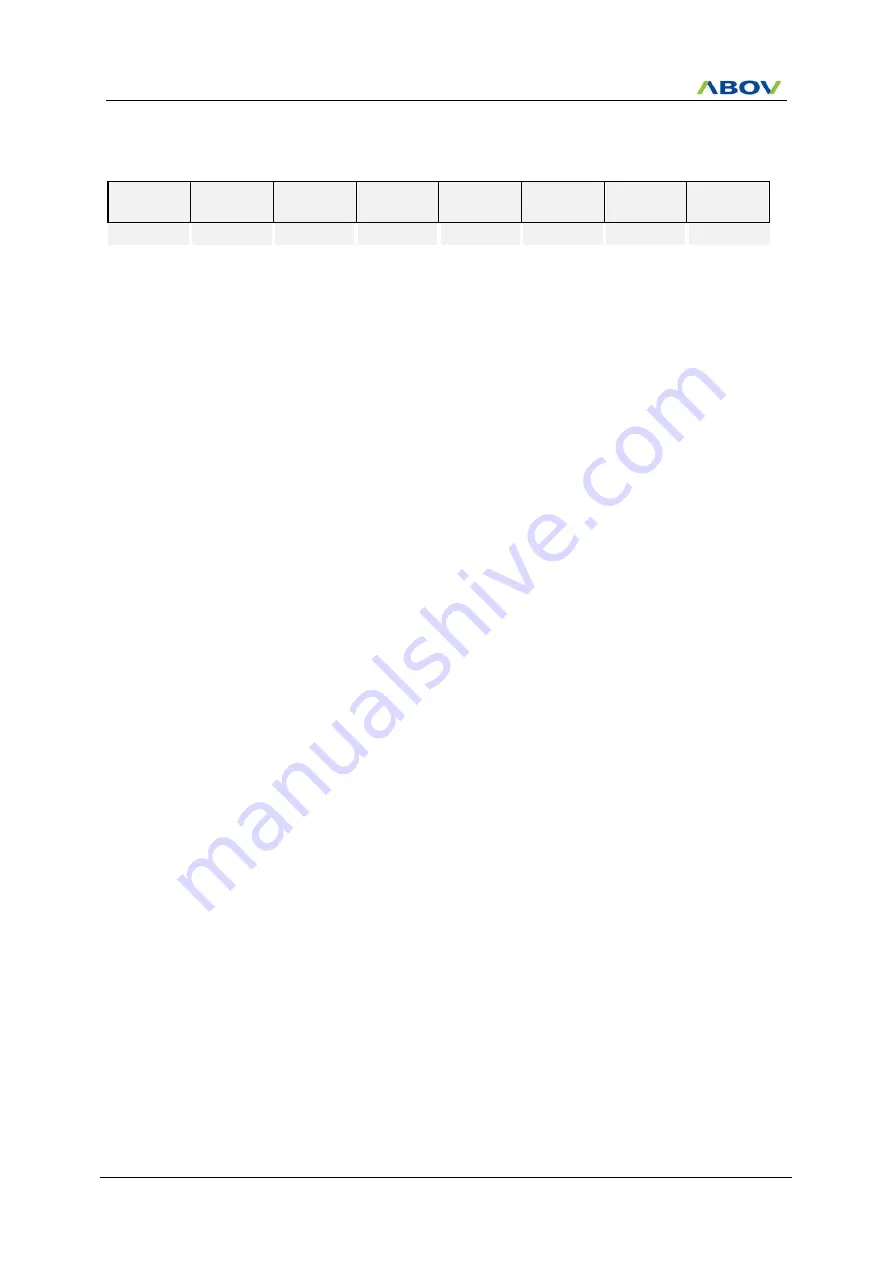

USI0CR1 (USI0 Control Register 1: For UART, SPI, and I2C mode) : D9H

7

6

5

4

3

2

1

0

USI0MS1

USI0MS0

USI0PM1

USI0PM0

USI0S2

USI0S1

ORD0

USI0S0

CPHA0

CPOL0

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

Initial value : 00H

USI0MS[1:0]

Selects operation mode of USI0

USI0MS1

USI0MS0

Operation mode

0

0

Asynchronous Mode (UART)

0

1

Synchronous Mode

1

0

I2C mode

1

1

SPI mode

USI0PM[1:0]

Selects parity generation and check methods (only UART mode)

USI0PM1

USI0PM0

Parity

0

0

No Parity

0

1

Reserved

1

0

Even Parity

1

1

Odd Parity

USI0S[2:0]

When in asynchronous or synchronous mode of operation,

selects the length of data bits in frame

USI0S2

USI0S1

USI0S0

Data Length

0

0

0

5 bit

0

0

1

6 bit

0

1

0

7 bit

0

1

1

8 bit

1

0

0

Reserved

1

0

1

Reserved

1

1

0

Reserved

1

1

1

9 bit

ORD0

This bit in the same bit position with USI0S1. The MSB of the data

byte is transmitted first when set to

‘1’ and the LSB when set to ‘0’

(only SPI mode)

0

LSB-first

1

MSB-first

CPHA0

This bit is in the same bit position with USI0S0. This bit determines if

data are sampled on the leading or trailing edge of SCK0 (only SPI

mode).

CPOL0

CPHA0

Leading edge

Trailing edge

0

0

Sample (Rising)

Setup (Falling)

0

1

Setup (Rising)

Sample (Falling)

1

0

Sample (Falling)

Setup (Rising)

1

1

Setup (Falling)

Sample (Rising)

CPOL0

This bit determines the clock polarity of ACK in synchronous or SPI

mode.

0

TXD change@Rising Edge, RXD change@Falling Edge

1

TXD change@Falling Edge, RXD change@Rising Edge

Summary of Contents for MC96F6432 Series

Page 24: ...MC96F6432 24 June 22 2018 Ver 2 9 4 Package Diagram Figure 4 1 48 Pin LQFP 0707 Package...

Page 25: ...MC96F6432 June 22 2018 Ver 2 9 25 Figure 4 2 44 Pin MQFP Package...

Page 26: ...MC96F6432 26 June 22 2018 Ver 2 9 Figure 4 3 32 Pin LQFP Package...

Page 27: ...MC96F6432 June 22 2018 Ver 2 9 27 Figure 4 4 32 Pin SOP Package...

Page 28: ...MC96F6432 28 June 22 2018 Ver 2 9 Figure 4 5 28 Pin SOP Package...