MC96F6432

June 22, 2018 Ver. 2.9

237

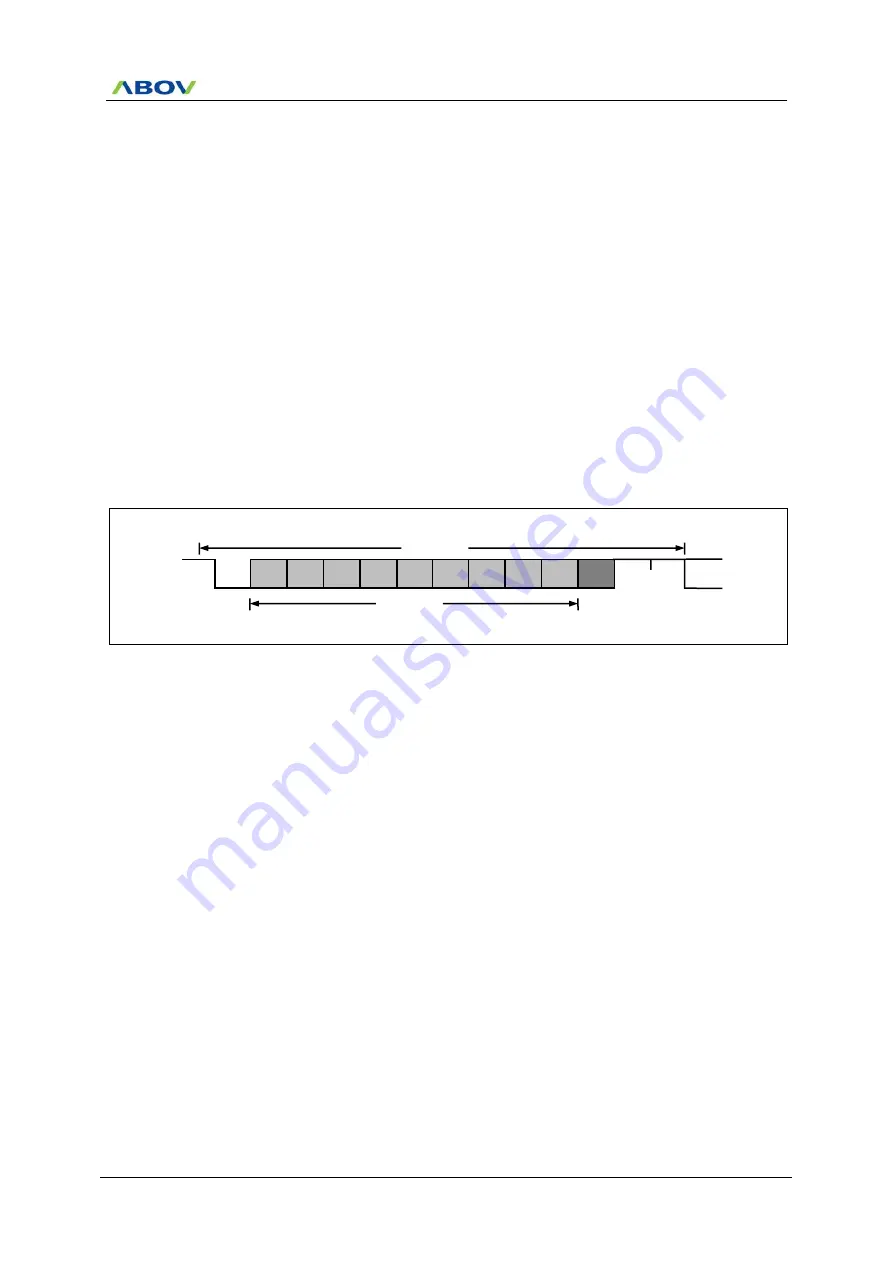

11.13.7 USI1 UART Data format

A serial frame is defined to be one character of data bits with synchronization bits (start and stop bits), and

optionally a parity bit for error detection.

The UART supports all 30 combinations of the following as valid frame formats.

- 1 start bit

- 5, 6, 7, 8 or 9 data bits

- no, even or odd parity bit

- 1 or 2 stop bits

A frame starts with the start bit followed by the least significant data bit (LSB). Then the next data bits, up to nine,

are succeeding, ending with the most significant bit (MSB). If parity function is enabled, the parity bit is inserted

between the last data bit and the stop bit. A high-to-low transition on data pin is considered as start bit.

When a

complete frame is transmitted, it can be directly followed by a new frame, or the communication line can be set to

an idle state. The idle means high state of data pin. The following figure shows the possible combinations of the

frame formats. Bits inside brackets are optional.

Figure 11.81 Frame Format (USI1)

1 data frame consists of the following bits

•

Idle No communication on communication line (TXD0/RXD0)

•

St Start bit (Low)

•

Dn Data bits (0~8)

•

Parity bit ------------ Even parity, Odd parity, No parity

•

Stop bit(s) ---------- 1 bit or 2 bits

The frame format used by the UART is set by the USI1S[2:0], USI1PM[1:0] bits in USI1CR1 register and

USI1SB bit in USI1CR3 register. The Transmitter and Receiver use the same setting.

11.13.8 USI1 UART Parity bit

The parity bit is calculated by doing an exclusive-OR of all the data bits. If odd parity is used, the result of the

exclusive-O is inverted. The parity bit is located between the MSB and first stop bit of a serial frame.

P

even

= D

n-1

^ … ^ D

3

^ D

2

^ D

1

^ D

0

^ 0

P

odd

= D

n-1

^ … ^ D

3

^ D

2

^ D

1

^ D

0

^ 1

P

even

: Parity bit using even parity

P

odd

: Parity bit using odd parity

D

n

: Data bit n of the character

[D7]

[D6]

[D5]

D4

D3

D2

D1

D0

[D8]

[P]

Idle

St

Sp1

[Sp2]

Idle / St

1 data frame

Character

bits

Summary of Contents for MC96F6432 Series

Page 24: ...MC96F6432 24 June 22 2018 Ver 2 9 4 Package Diagram Figure 4 1 48 Pin LQFP 0707 Package...

Page 25: ...MC96F6432 June 22 2018 Ver 2 9 25 Figure 4 2 44 Pin MQFP Package...

Page 26: ...MC96F6432 26 June 22 2018 Ver 2 9 Figure 4 3 32 Pin LQFP Package...

Page 27: ...MC96F6432 June 22 2018 Ver 2 9 27 Figure 4 4 32 Pin SOP Package...

Page 28: ...MC96F6432 28 June 22 2018 Ver 2 9 Figure 4 5 28 Pin SOP Package...