MC96F6432

June 22, 2018 Ver. 2.9

293

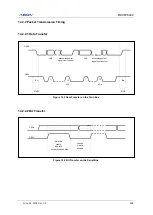

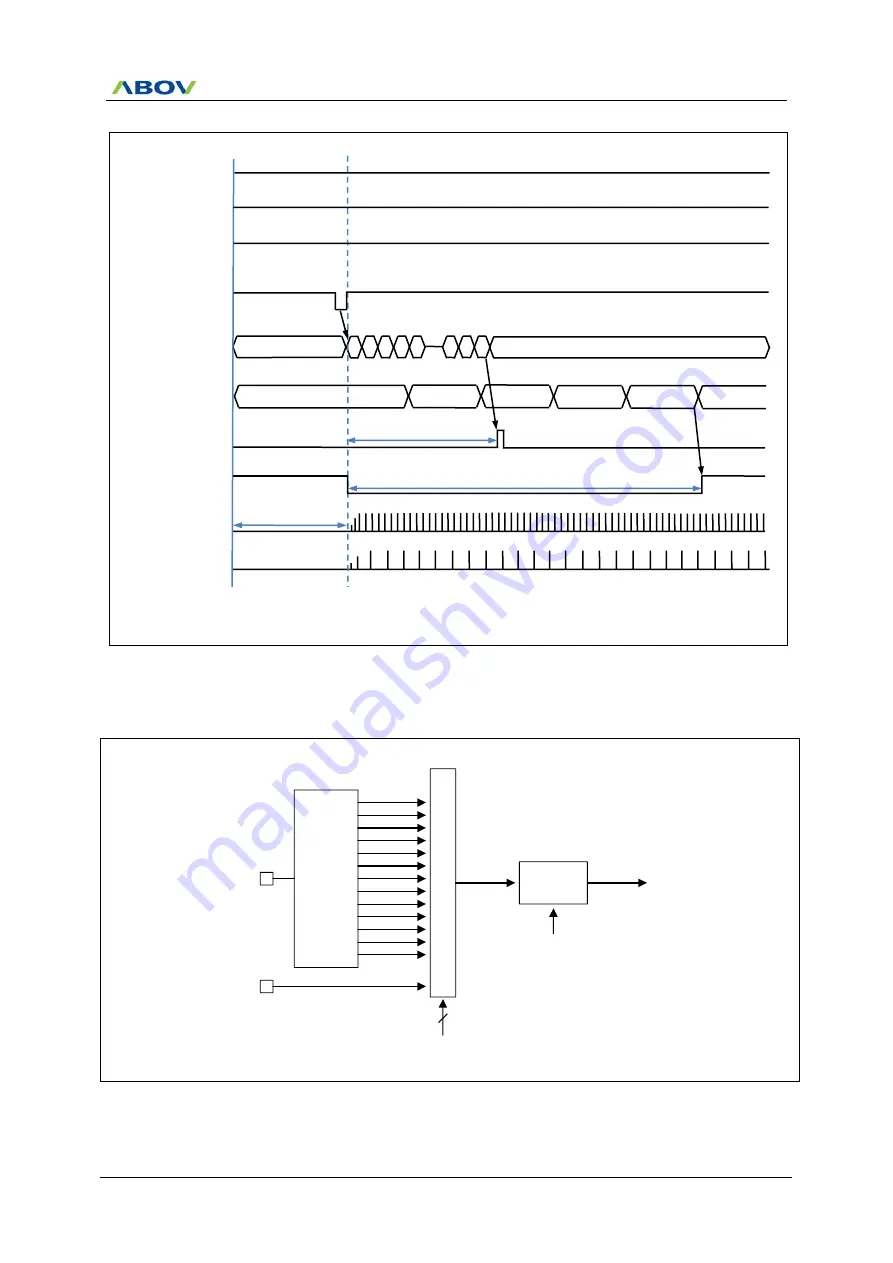

Figure 13.11 Configuration timing when BOD RESET

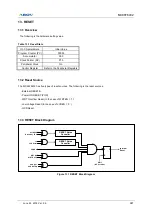

13.8 LVI Block Diagram

M

U

X

LVIF

LVIEN

2.44V

VDD

LVIREF

Reference

Voltage

Generator

2.59V

2.75V

LVI Circuit

LVILS[3:0]

2.93V

3.14V

3.38V

3.67V

4.00V

4.40V

2.10V

2.20V

2.32V

2.00V

4

Figure 13.12 LVI Diagram

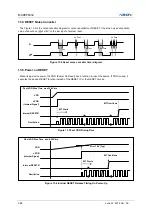

VDD

Internal nPOR

PAD RESETB

BIT (for Config)

LVR_RESETB

BIT (for Reset)

INT-OSC 8MHz/8

INT-OSC (8MHz)

RESET_SYSB

Config Read

1us X 256 X 28h = about 10ms

1us X 4096 X 4h = about 16ms

F1

00

01

02

00

..

..

..

27

28

F1

“H”

INT-OSC 8MHz / 8 = 1MHz (1us)

“H”

“H”

Main OSC Off

01

02

03

04

00

Summary of Contents for MC96F6432 Series

Page 24: ...MC96F6432 24 June 22 2018 Ver 2 9 4 Package Diagram Figure 4 1 48 Pin LQFP 0707 Package...

Page 25: ...MC96F6432 June 22 2018 Ver 2 9 25 Figure 4 2 44 Pin MQFP Package...

Page 26: ...MC96F6432 26 June 22 2018 Ver 2 9 Figure 4 3 32 Pin LQFP Package...

Page 27: ...MC96F6432 June 22 2018 Ver 2 9 27 Figure 4 4 32 Pin SOP Package...

Page 28: ...MC96F6432 28 June 22 2018 Ver 2 9 Figure 4 5 28 Pin SOP Package...