MC96F6432

June 22, 2018 Ver. 2.9

33

Table 5-1 Normal Pin Description (Continued)

PIN

Name

I/O

Function

@RESET

Shared with

RESETB

I/O

System reset pin with a pull-up resistor when it

is selected as the RESETB by CONFIGURE

OPTION

Input

P55

DSDA

I/O

On chip debugger data input/output

(NOTE4,5)

Input

P00/EC3

DSCL

I/O

On chip debugger clock input

(NOTE4,5)

Input

P01/T3O

XIN

I/O

Main oscillator pins

Input

P51

XOUT

P50

SXIN

I/O

Sub oscillator pins

Input

P53/T0O/PWM0O

SXOUT

P54/EINT10

VDD,

VSS

–

Power input pins

–

–

NOTES) 1. The P14

–P17, P23–P25, P34–P37, and P43 are not in the 32-pin package.

2.

The P13

–P17, P22–P27, P34–P37, and P43 are not in the 28-pin package.

3.

The P55/RESETB pin is configured as one of the P55 and RESETB pin by the

“CONFIGURE

OPTION.

”

4.

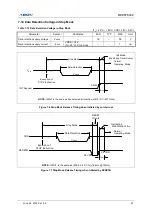

If the P00/EC3/DSDA and P01/T3O/DSCL pins are connected to an emulator during the resistor

power-on reset, the pins are automatically configured as the debugger pins.

5.

The P00/EC3/DSDA and P01/T3O/DSCL pins are configured as inputs with internal pull-up resistor

only during the reset or power-on reset.

6.

The P50/XOUT, P51/XIN, P53/SXINT/T0O/PWM0O, and P54/SXOUT/EINT10 pins are

configured as a function pin by software control.

Summary of Contents for MC96F6432 Series

Page 24: ...MC96F6432 24 June 22 2018 Ver 2 9 4 Package Diagram Figure 4 1 48 Pin LQFP 0707 Package...

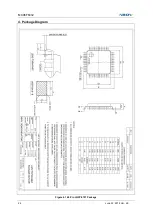

Page 25: ...MC96F6432 June 22 2018 Ver 2 9 25 Figure 4 2 44 Pin MQFP Package...

Page 26: ...MC96F6432 26 June 22 2018 Ver 2 9 Figure 4 3 32 Pin LQFP Package...

Page 27: ...MC96F6432 June 22 2018 Ver 2 9 27 Figure 4 4 32 Pin SOP Package...

Page 28: ...MC96F6432 28 June 22 2018 Ver 2 9 Figure 4 5 28 Pin SOP Package...