MC96F6432

June 22, 2018 Ver. 2.9

95

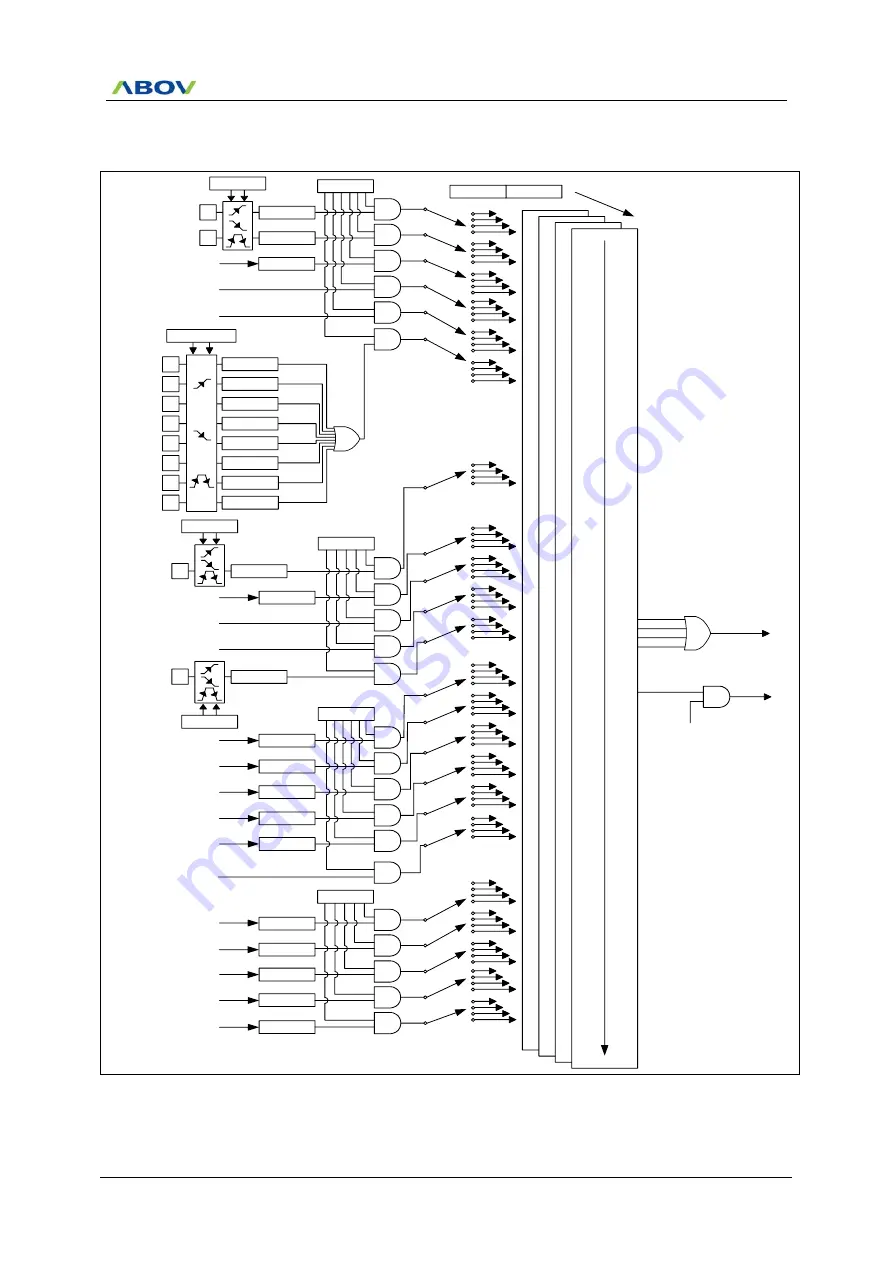

10.3 Block Diagram

0

0

0

0

Priority High

1

1

1

1

2

2

2

2

3

3

3

3

4

4

4

4

5

5

5

5

6

6

6

6

7

7

7

7

8

8

8

8

9

9

9

9

10

10

10

10

11

11

11

11

12

12

12

12

13

13

13

13

14

14

14

14

15

15

15

15

16

16

16

16

17

17

17

17

18

18

18

18

19

19

19

19

20

20

20

20

21

21

21

21

22

22

22

22

23

23

23

23

Priority Low

EA

Release

Stop/Sleep

EINT10

EIFLAG1.1

EIFLAG1.2

EINT11

EINT1

EIFLAG0.0

EINT3

EINT5

EINT7

EINT0

EINT2

EINT4

EINT6

EIFLAG0.1

EIFLAG0.2

EIFLAG0.3

EIFLAG0.4

EIFLAG0.5

EIFLAG0.6

EIFLAG0.7

Timer 0 overflow

Timer 0

Timer 1

Timer 2

Timer 3

IP1

IP

IE

FLAG10

FLAG11

IE2

T0OVIFR

T0IFR

T1IFR

T2IFR

T3IFR

FLAG0

FLAG1

FLAG2

FLAG3

FLAG4

FLAG5

FLAG6

FLAG7

EIPOL1

USI0 I2C

USI0 Rx

USI0 Tx

IE1

I2C0IFR

ADC

WT

WDT

BIT

ADCIFR

WTIFR

WDTIFR

BITIFR

Level 0

Level 1

Level 2

Level 3

EIPOL0H/L

USI1 I2C

USI1 Rx

USI1 Tx

I2C1IFR

SPI2

SPIIFR

EINT12

EIFLAG1.3

FLAG12

EIPOL1

IE3

EINT8

EIFLAG1.0

FLAG8

EIPOL1

Timer 4

Figure 10.2 Block Diagram of Interrupt

NOTES) 1. The release signal for stop/idle mode may be generated by all interrupt sources which are enabled

without reference to the priority level.

2. An interrupt request is delayed while data are written to IE, IE1, IE2, IE3, IP, IP1, and PCON register.

Summary of Contents for MC96F6432 Series

Page 24: ...MC96F6432 24 June 22 2018 Ver 2 9 4 Package Diagram Figure 4 1 48 Pin LQFP 0707 Package...

Page 25: ...MC96F6432 June 22 2018 Ver 2 9 25 Figure 4 2 44 Pin MQFP Package...

Page 26: ...MC96F6432 26 June 22 2018 Ver 2 9 Figure 4 3 32 Pin LQFP Package...

Page 27: ...MC96F6432 June 22 2018 Ver 2 9 27 Figure 4 4 32 Pin SOP Package...

Page 28: ...MC96F6432 28 June 22 2018 Ver 2 9 Figure 4 5 28 Pin SOP Package...