MC96F6432

June 22, 2018 Ver. 2.9

99

10.7 Multi Interrupt

If two requests of different priority levels are received simultaneously, the request of higher priority level is

served first. If more than one interrupt request are received, the interrupt polling sequence determines which

request is served first by hardware. However, for special features, multi-interrupt processing can be executed by

software.

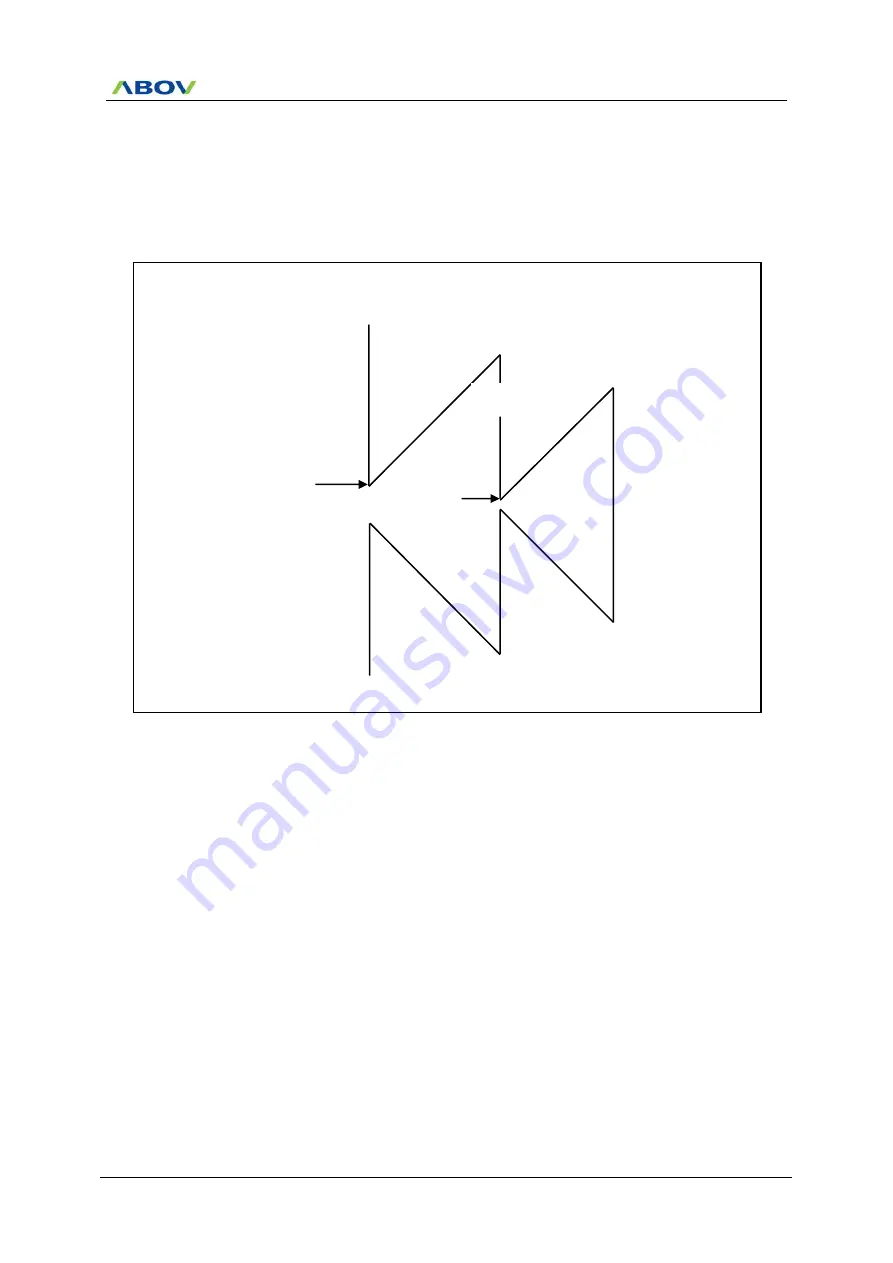

Figure 10.6 Effective Timing of Multi-Interrupt

Figure 10.6 shows an example of multi-interrupt processing. While INT1 is served, INT0 which has higher

priority than INT1 is occurred. Then INT0 is served immediately and then the remain part of INT1 service routine

is executed. If the priority level of INT0 is same or lower than INT1, INT0 will be served after the INT1 service has

completed.

An interrupt service routine may be only interrupted by an interrupt of higher priority and, if two interrupts of

different priority occur at the same time, the higher level interrupt will be served first. An interrupt cannot be

interrupted by another interrupt of the same or a lower priority level. If two interrupts of the same priority level

occur simultaneously, the service order for those interrupts is determined by the scan order.

Main Program

Service

Occur

INT1 Interrupt

INT1 ISR

Occur

INT0 Interrupt

INT0 ISR

RETI

RETI

Set EA

Summary of Contents for MC96F6432 Series

Page 24: ...MC96F6432 24 June 22 2018 Ver 2 9 4 Package Diagram Figure 4 1 48 Pin LQFP 0707 Package...

Page 25: ...MC96F6432 June 22 2018 Ver 2 9 25 Figure 4 2 44 Pin MQFP Package...

Page 26: ...MC96F6432 26 June 22 2018 Ver 2 9 Figure 4 3 32 Pin LQFP Package...

Page 27: ...MC96F6432 June 22 2018 Ver 2 9 27 Figure 4 4 32 Pin SOP Package...

Page 28: ...MC96F6432 28 June 22 2018 Ver 2 9 Figure 4 5 28 Pin SOP Package...