MC96FM204/FM214

April 7, 2016 Ver. 1.8

137

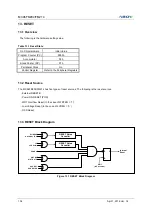

Table 13-2 Boot Process Description

Process

Description

Remarks

①

-No Operation

②

-1st POR level Detection

-about 1.4V

③

- (INT-OSC 8MHz/8)x256x28h Delay section (=10ms)

-VDD input voltage must rise over than flash operating

voltage for Config read

-Slew Rate

>=

0.05V/ms

④

- Config read point

-over 1.75V

-Config Value is determined by

Writing Option

⑤

- Rising section to Reset Release Level

-16ms point after POR or Ext_reset

release

⑥

- Reset Release section (BIT overflow)

i) after16ms, after External Reset Release (External reset)

ii) 16ms point after POR (POR only)

- BIT is used for Peripheral stability

⑦

-Normal operation

Summary of Contents for MC96FM204

Page 17: ...MC96FM204 FM214 April 7 2016 Ver 1 8 17 4 Package Diagram Figure 4 1 20 Pin SOP Package ...

Page 18: ...MC96FM204 FM214 18 April 7 2016 Ver 1 8 Figure 4 2 20 Pin TSSOP Package ...

Page 19: ...MC96FM204 FM214 April 7 2016 Ver 1 8 19 Figure 4 3 16 Pin SOP Package ...

Page 20: ...MC96FM204 FM214 20 April 7 2016 Ver 1 8 Figure 4 4 16 Pin TSSOP Package ...