MC97F6108A User’s manual

11. PPG (Programmable Pulse Generator)

101

11.6

Disable PPG output by comparator 3

PPGMD

4 us

2 us

8 us

by pass

100

011

010

CAPE

PPGH/L (16-bit Counter)

DUTY Compare

REGISTER

C

le

a

r &

S

ta

rt

PERIOD Compare

REGISTER

S

R

Q

clear

PPG_PE

PPGO

PPGCH/L

PPGIN[2:0]

3

DETC3EN

clear

PPG_CLK

CMP1IF

CIEDGE[3]

CIPOLA[3]

CIBOTH[3]

CMP3IF

CIENAB[3]

-

+

CMP3

by pass

0.3 us

0.6 us

1.2 us

C3DBSEL[1:0]

CFEDGE[3]

CFPOLA[3]

CFBOTH[3]

CFENAB[3]

CMP4IF

C3_FLAG

PPG

PPGO3DB[1:0]

PPGO on/off-time detect

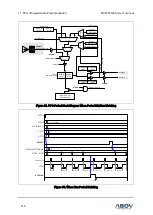

Figure 39. Disable PPG Output Block Diagram by Comparator 3

PPG output is disabled by comparator 3 flag (C3_FLAG) with enable bit DETC3EN in the PPGCR2

register. When DETC3EN is set and comparator 3 output occurs, PPG outputs its default value. Then

C3_FLAG is cleared when PPG output is disabled. C3_FLAG can be cleared by writting '0'.

Specified period of time after the PPGO goes to low and PPG is disabled (PPGO = 'high') C3_FLAG is

not generated. The time is determined by PPGO3DB register in CA_REGC. To generate C3_FLAG,

PPGMD need to be '1'.

C3_FLAG

DUTY

start pulse

PPGO

PERIOD

PERIOD

on-time

DUTY

off-time

Comparator 3

output

PPGIF

TPPGOen

PPGMD

DETC3EN

DETC1EN

-

-

-

PPGCR2

ADDRESS :

E1

H

Figure 40. Disable PPG Output by Comparator 3 (C3_FLAG)