ACCES I/O Products, Inc.

MADE IN THE USA

PCIe-ADIO16-16F Family Manual

3

Rev B3d

All configuration of this device is performed through software; there

are no jumpers or switches to set.

C

HAPTER

5:

PC

I

NTERFACE

This product interfaces with a PC using a PCI Express Gen 2 1×lane

connection.

C

HAPTER

6:

I/O

I

NTERFACE

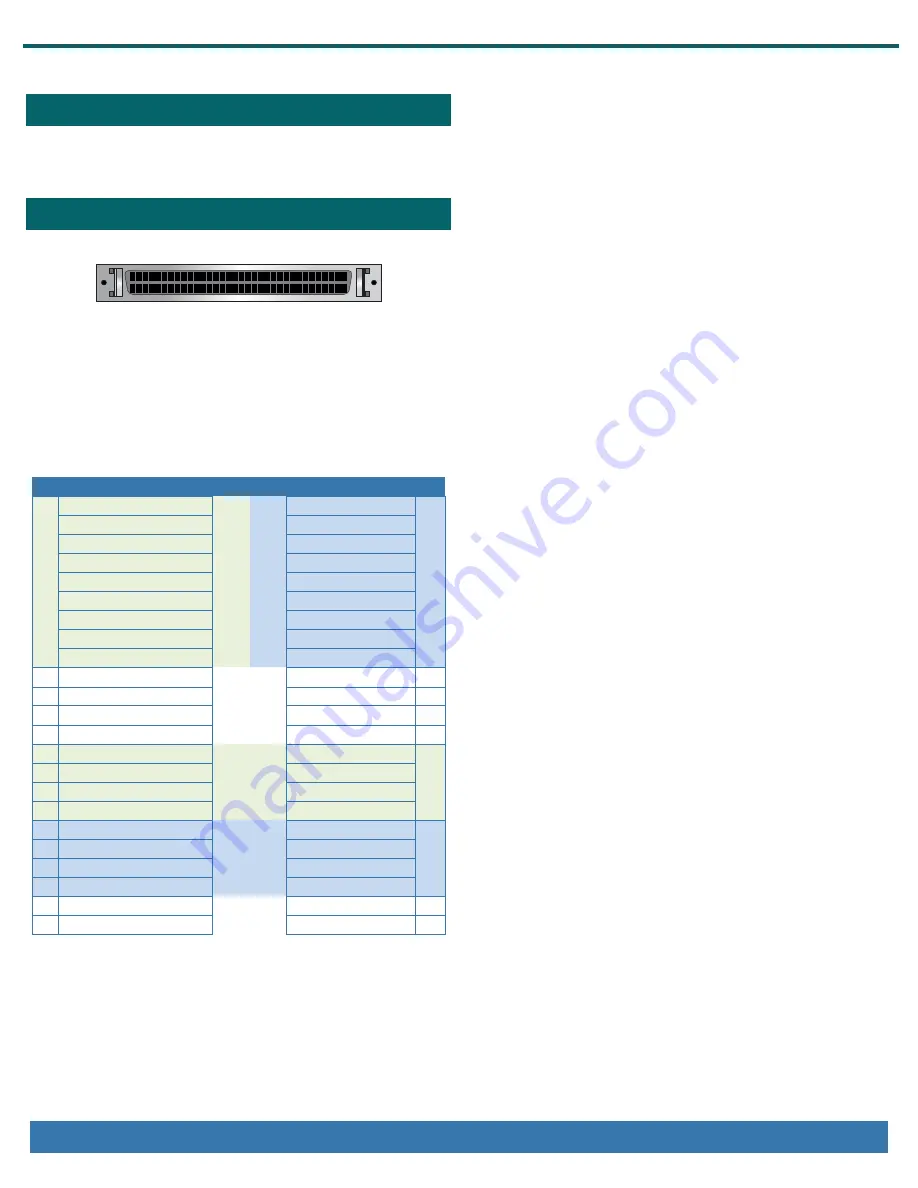

The 68-Pin connector provides all I/O signals for the board:

For Singled-Ended analog inputs connect GND to ADC COMMON.

A Note About Unused Analog Inputs:

Any unused analog input should be connected to ground with a

short jumper wire; either in the mating connector cable, or on the

breakout terminal board. This will reduce / eliminate crosstalk

which, if left unchecked, can influence measurements of adjacent

connected

input channels.

68-Pin SCSI Female, Latched

AD

AS

3022 #

0

S.

E.

(D

iff.

)

ADC IN 0 (Ch 0+) 1

35 ADC IN 1 (Ch 0-)

AD

AS

3022 #

1

ADC IN 2 (Ch 1+) 3

37 ADC IN 3 (Ch 1-)

ADC IN 4 (Ch 2+) 5

39 ADC IN 5 (Ch 2-)

ADC IN 6 (Ch 3+) 7

41 ADC IN 7 (Ch 3-)

ADC IN 8 (Ch 4+) 9

43 ADC IN 9 (Ch 4-)

ADC IN 10 (Ch 5+) 11

45 ADC IN 11 (Ch 5-)

ADC IN 12 (Ch 6+) 13

47 ADC IN 13 (Ch 6-)

ADC IN 14 (Ch 7+) 15

49 ADC IN 15 (Ch 7-)

ADC1 COMMON 17

51 ADC2 COMMON

DAC 0 19

53 DAC2

DAC 1 21

55 DAC 3

Digital Ground 23

57 Digital Ground

Digital Ground 24

58 Digital Ground

DIO BitIndex 14 25

59 DIO BitIndex 15

Gr

ou

p 1

DIO BitIndex 12 26

60 DIO BitIndex 13

DIO BitIndex 10 27

61 DIO BitIndex 11

DIO BitIndex 8 28

62 DIO BitIndex 9

DIO BitIndex 6 29

63 DIO BitIndex 7

Gr

ou

p 0

DIO BitIndex 4 30

64 DIO BitIndex 5

DIO BitIndex 2 31

65 DIO BitIndex 3

DIO BitIndex 0 32

66 DIO BitIndex 1

Digital Ground 33

67 Digital Ground

VCCdio

1

/ UserVCCdio 34

68 Watchdog Active

1

: VCCio pin outputs fused 3.3VDC @ 0.5A on standard models.

-VCCIO option converts VCCio into a user input between 1.65VDC

and 5.5VDC.

All unlisted pins in the above table are analog ground.