Appendix

D Clock Modes

Installation and Operation Manual

D-4

PSN Clock Recovery

ACE-3105, ACE-3205 Ver. 5.2

D.4

PSN Clock Recovery

The PSN clock recovery algorithm is based on the packet inter-arrival time. In

order to compensate for packet delay variation and network jitter, the clock

recovery mechanism has a fixed-size jitter buffer. In addition, the clock stream

can be prioritized per configuration.

The quality of the recovered clock is defined by five compliance levels: Stratum-1,

Stratum-2, Stratum-3, Struaum-3E and Stratum-4. The compliance level is

user-configurable.

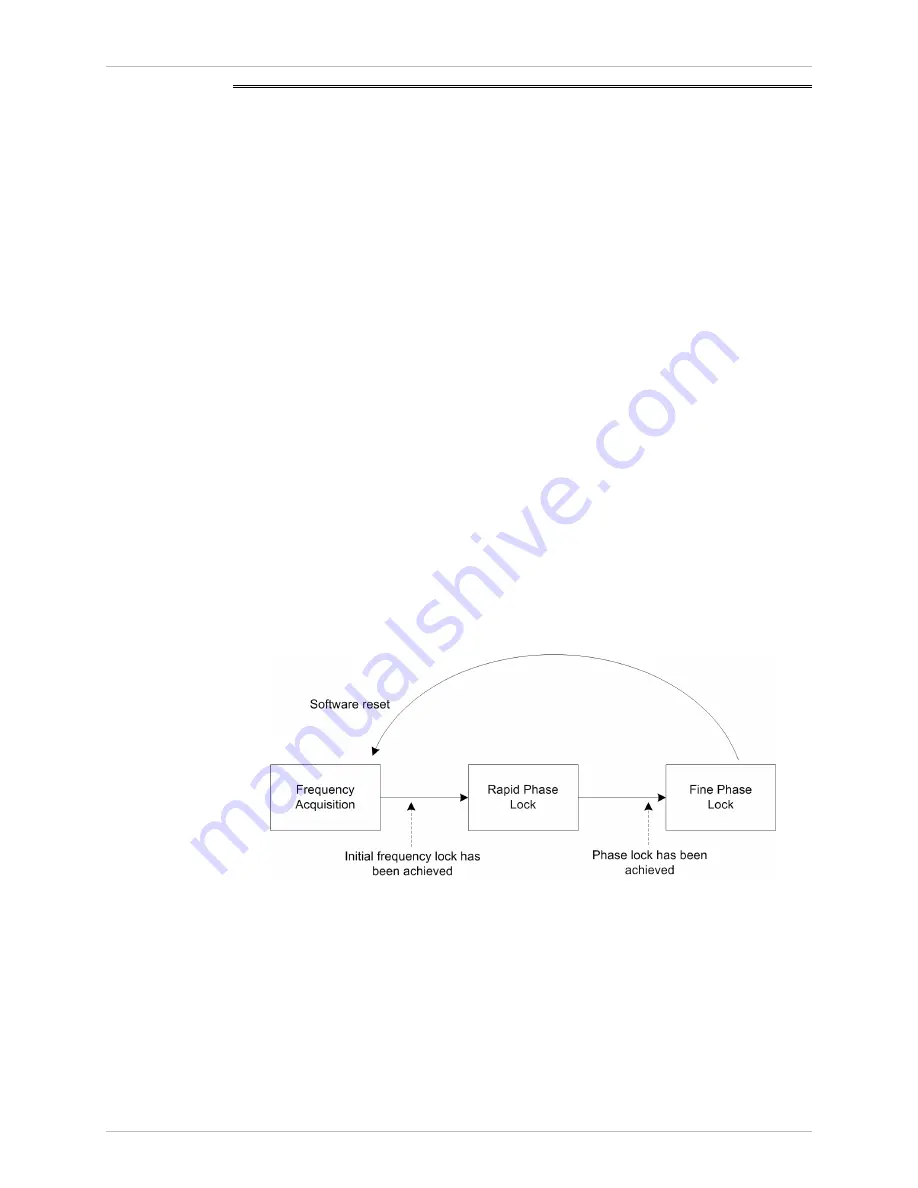

There are four clock recovery states:

•

Frequency Acquisition – When the clock recovery chip starts receiving good

clock packets in Stratum-3 or Stratum-4 mode, this pre-tracking state is

applied for fast frequency learning.

•

Rapid Phase Lock – The clock recovery chip is learning the phase of the

packet-based clock stream. This state may take several minutes depending on

the impact of the PSN with which the device communicates. Once the clock

phase is learned, the Fine Phase Lock state starts.

•

Fine Phase Lock – The clock phase has been learned and the device is locked

on a steady and reliable clock stream.

•

Holdover – The clock PW link is down and the clock recovery mechanism is

locked on the last frequency it previously acquired. For more information, see

below.

The following figure illustrates the process of shifting between clock recovery

states:

Figure

D-2. Clock Recovery States

Holdover State

When the clock PW is down (physical or logical setback), the clock mechanism

enters into a 'Holdover' state, which keeps the last known good clock frequency

while waiting for any condition change.