Major Chips Description

2-79

2.7.4

Pin Description

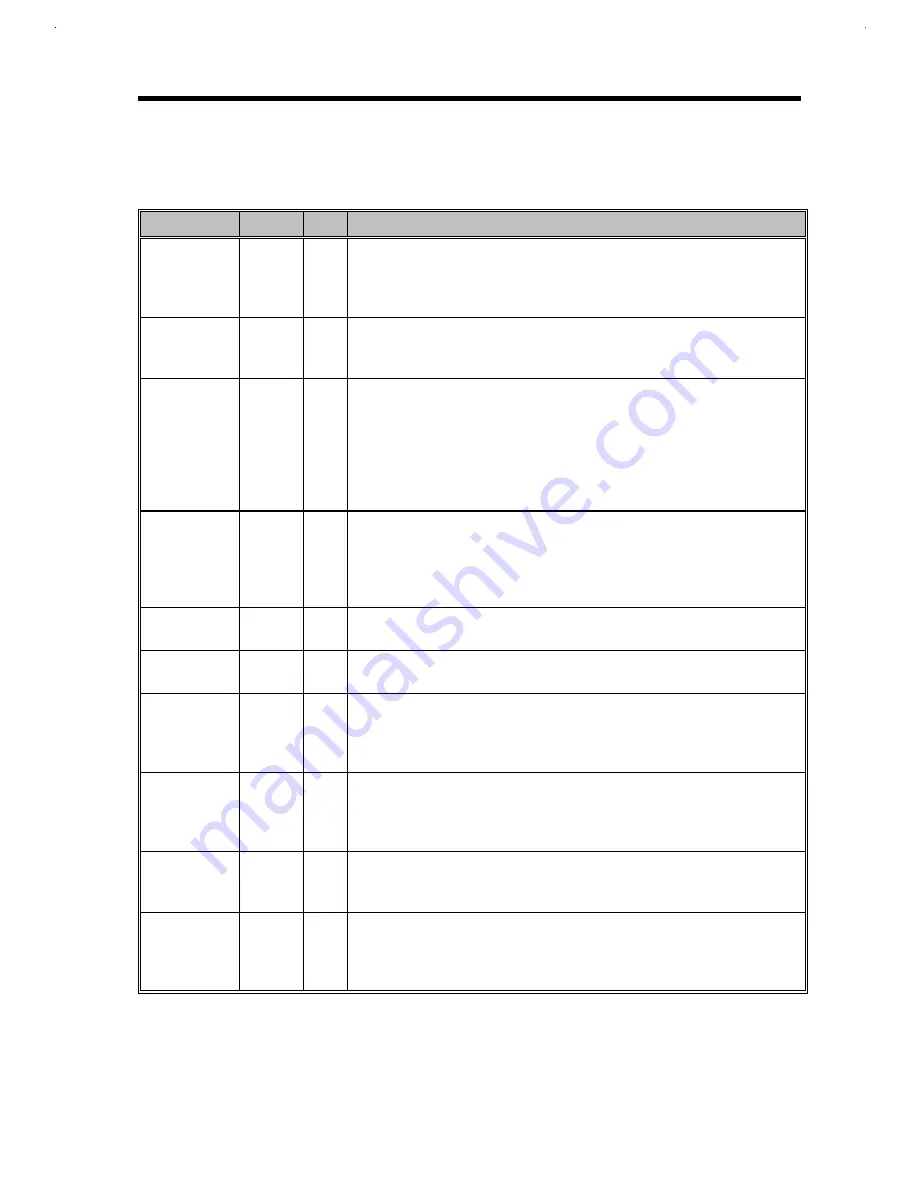

Table 2-14

NS87336VJG Pin Descriptions

Pin

No.

I/O

Description

A15-A0

67, 64,

62-60,

29, 19-

28

I

Address. These address lines from the microprocessor determine which

internal register is accessed. A0-A15 are don't cares during DMA

transfer.

/ACK

83

I

Parallel Port Acknowledge. This input is pulsed low by the printer to

indicate that it has received the data from the parallel port. This pin has

a nominal 25 K

Ω

pull-up resistor attached to it.

ADRATE0,

ADRATE1

96,

46

O

FDD Additional Data Rate 0,1. These outputs are similar to DRATE0, 1.

They are provided in addition to DRATE0, 1. They reflect the currently

selected FDC data rate, (bits 0 and 1 in the Configuration Control

Register (CCR) or the Data Rate Select Register (DSR), whichever was

written to last). ADRATE0 is configured when bit 0 of ASC is 1.

ADRATE1 is configured when bit 4 of ASC is 1. (See IRQ5 and

DENSEL for further information).

/AFD

76

I/O

Parallel Port Automatic Feed XT. When this signal is low, the printer

automatically line feed after printing each line. This pin is in a tristate

condition 10 ns after a 0 is loaded into the corresponding Control

Register bit. The system should pull this pin high using a 4.7 K

Ω

resistor.

AEN

18

I

Address Enable. When this input is high, it disables function selection

via A15-A0. Access during DMA transfer is not affected by this pin.

/ASTRB

79

O

EPP Address Strobe. This signal is used in EPP mode as address

strobe. It is an active low signal.

BADDR0,

BADDR1

72,

71

I

Base Address. These bits determine one of the four base addresses

from which the Index and Data Registers are offset. An internal pull-

down resistor of 30 K

Ω

is on this pin. Use a 10 K

Ω

resistor to pull this

pin to VCC.

BOUT1,

BOUT2

71,

63

O

UARTs Baud Output. This multi-function pin supports the associated

serial channel Baud Rate generator output signal if the test mode is

selected in the Power and Test Configuration Register and the DLAB bit

(LCR7) is set. After the Master Reset, this pin offers the SOUT function.

BUSY

82

I

Parallel Port Busy. This pin is set high by the printer when it cannot

accept another character. It has a nominal 25 K

Ω

pull-down resistor

attached to it.

CFG0

CFG1

63,

69

I

Configuration on Power-up. These CMOS inputs select 1 of 4 default

configurations in which the PC87336 powers up. An internal pull-down

resistor of 30 K

Ω

is on each pin. Use a 10 K

Ω

resistor to pull these pins

to VCC.

Summary of Contents for AcerNote Light 370P

Page 6: ...vi ...

Page 26: ...1 8 Service Guide Figure 1 5 Main Board Layout Bottom Side ...

Page 49: ...System Introduction 1 31 1 5 1 3 Power Management Figure 1 14 Power Management Block Diagram ...

Page 55: ...System Introduction 1 37 1 6 System Block Diagram Figure 1 15 System Block Diagram ...

Page 64: ...Major Chips Description 2 7 2 2 5 Pin Diagram Figure 2 4 M1521 Pin Diagram ...

Page 99: ...2 42 Service Guide 2 5 3 Pin Diagram Figure 2 10 C T 65550 Pin Diagram ...

Page 117: ...2 60 Service Guide Figure 2 12 Functional block diagram CardBus Card Interface ...

Page 119: ...2 62 Service Guide Figure 2 14 PCI to CardBus terminal assignments ...

Page 135: ...2 78 Service Guide 2 7 3 Pin Diagram Figure 2 16 NS87336VJG Pin Diagram ...

Page 145: ...2 88 Service Guide 2 8 2 Pin Diagram Figure 2 17 YMF715 Block Diagram ...

Page 185: ...Disassembly and Unit Replacement 4 5 Figure 4 3 Disassembly Sequence Flowchart ...

Page 209: ...B 2 Service Guide ...

Page 210: ...Exploded View Diagram B 3 ...