Troubleshooting

4-21

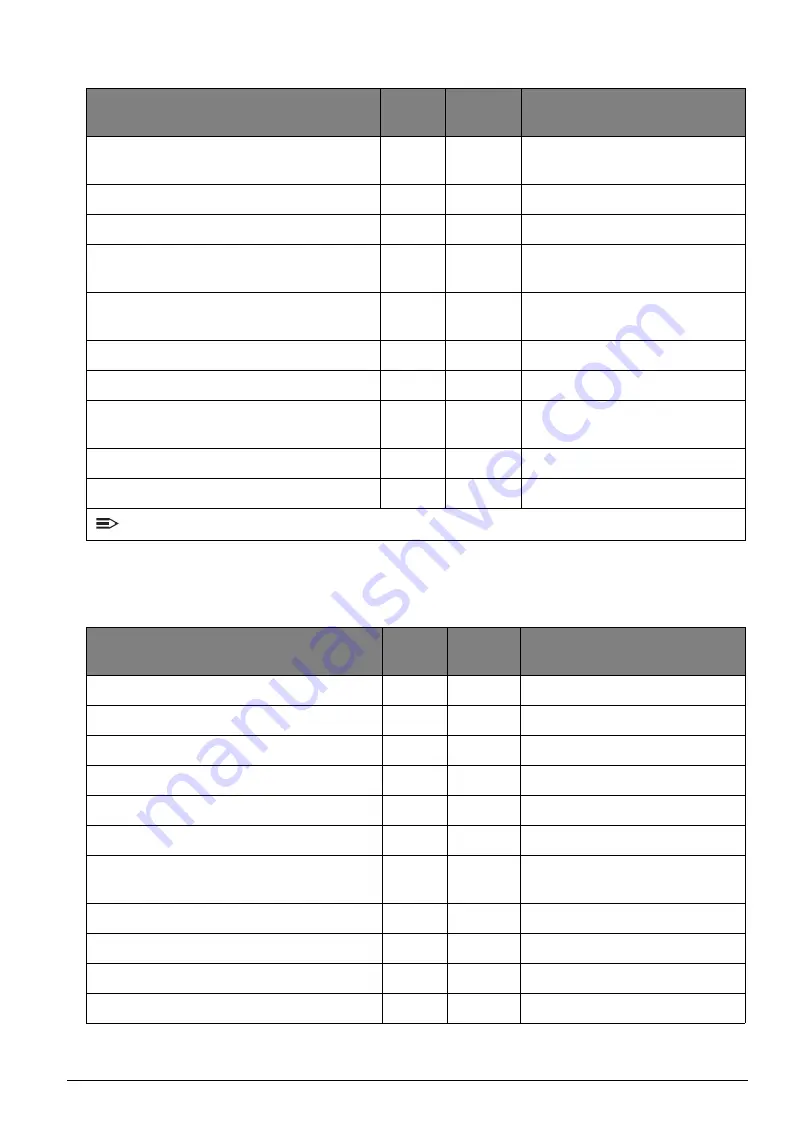

Table 4-3. SEC Phase POST Code Table

Table 4-4. PEI Phase POST Code Table

Functionality Name

(Include\PostCode.h)

Phase

Post

Code

Description

SEC_SYSTEM_POWER_ON

SEC

01

CPU power on and switch to

Protected mode

SEC_BEFORE_MICROCODE_PATCH

SEC

02

Patching CPU microcode

SEC_AFTER_MICROCODE_PATCH

SEC

03

Setup Cache as RAM

SEC_ACCESS_CSR*

SEC

04

PCIE MMIO Base Address

initial

SEC_GENERIC_MSRINIT*

SEC

05

CPU Generic MSR

initialization

SEC_CPU_SPEEDCFG*

SEC

06

Setup CPU speed

SEC_SETUP_CAR_OK

SEC

07

Cache as RAM test

SEC_FORCE_MAX_RATIO*

SEC

08

Tune CPU frequency ratio to

maximum level

SEC_GO_TO_SECSTARTUP

SEC

09

Setup BIOS ROM cache

SEC_GO_TO_PEICORE

SEC

0A

Enter Boot Firmware Volume

NOTE:

* 3rd party relate functions - Platform dependence.

Functionality Name

(Include\PostCode.h)

Phase

Post

Code

Description

PEI_SIO_INIT

PEI

70

Super I/O Initialization

PEI_CPU_REG_INIT

PEI

71

CPU Early Initialization

PEI_CPU_AP_INIT*

PEI

72

Multi-processor Early Initial

PEI_CPU_HT_RESET*

PEI

73

HyperTransport Initialization

PEI_PCIE_MMIO_INIT

PEI

74

PCIE MMIO BAR Initialization

PEI_NB_REG_INIT

PEI

75

North Bridge Early Initialization

PEI_SB_REG_INIT

PEI

76

South Bridge Early

Initialization

PEI_PCIE_TRAINING*

PEI

77

PCIE Training

PEI_TPM_INIT

PEI

78

TPM Initialization

PEI_SMBUS_INIT

PEI

79

SMBUS Early Initialization

PEI_PROGRAM_CLOCK_GEN

PEI

7A

Clock Generator Initialization