1-

32

Service Guide

ON MODE

Normal full-on operation

STANDBY MODE

The notebook consumes very low power in standby mode. Data remain intact in the system memory until

battery is drained.

The necessary condition for the notebook to enter standby mode is that the reserved disk space size for

saving system and video memory is insufficient so the notebook is unable to enter hibernation mode. In this

situation, there are three ways to enter standby mode:

•

Press the standby/hibernation hotkey Fn-F7 ( )

•

Set a value for the System Standby/Hibernation Timer in Setup. If the waiting time specified by this

timer elapses without any system activity, the notebook goes into standby mode.

•

Invoked by the operating system power saving modes

The following signals indicate that the notebook is in standby mode:

•

The buzzer beeps (when you press the standby/hibernation hotkey)

•

The indicator light flashes

To leave standby mode and return to normal mode, press the any key. If an incoming PCMCIA modem

event occurs and the Modem Ring Wake Up From Standby is enabled, the system returns to normal mode.

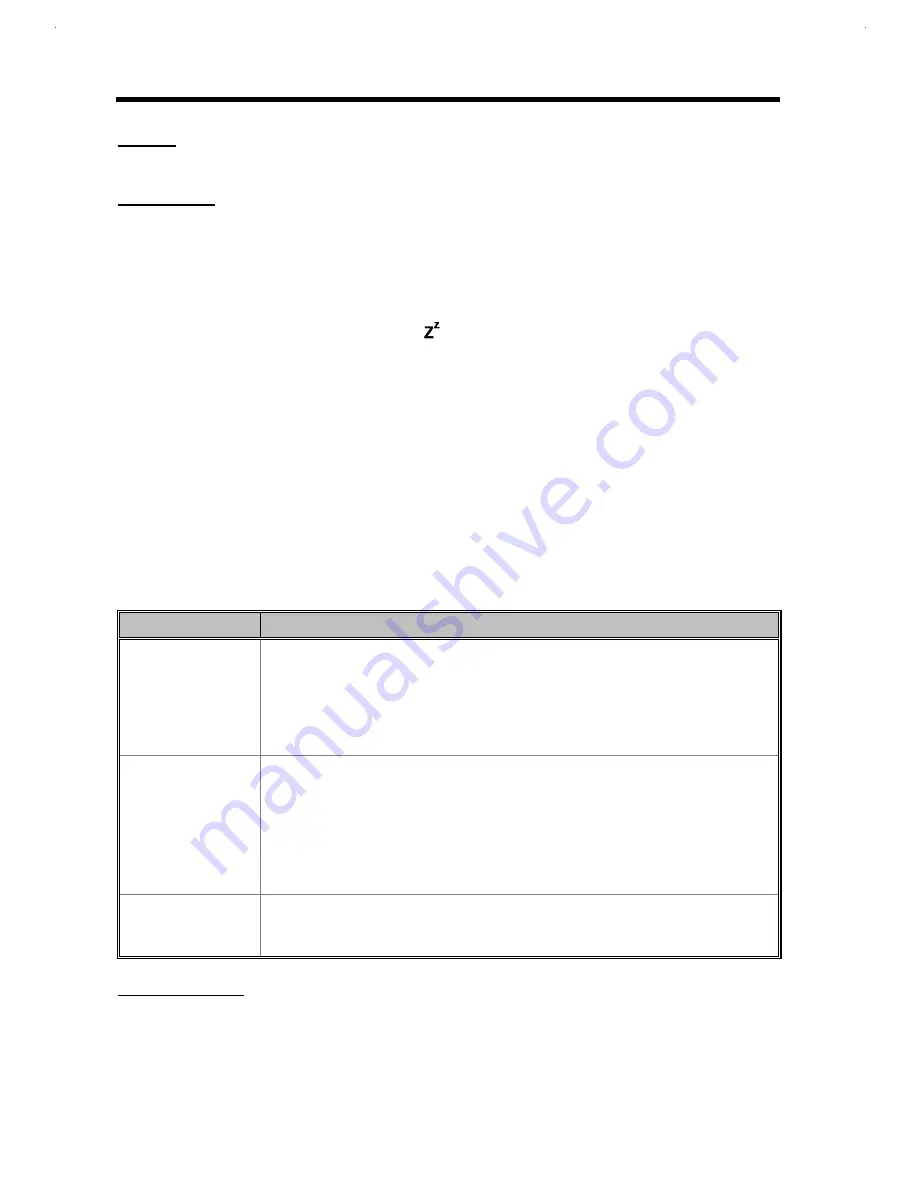

Table 1-36

Standby Mode Conditions and Descriptions

Condition

Description

The condition to enter

Standby Mode

•

“Hard Disk Drive” is [Disabled] in System Security of BIOS SETUP.

•

“Hard Disk 0” is [None] in Basic System Configuration of BIOS SETUP.

•

HDD has not located enough free contiguous disk space generated by Sleep Manager

and this free space is not corrupted.

•

Standby/Hibernation Timer times-out or Standby/Hibernation HotKey pressed and

there is no activity within 1/2 second.

The condition of

Standby Mode

•

Issue a beep.

•

Flash standby LED with 1 Hz frequency.

•

Disable the mouse, serial and the parallel port.

•

The keyboard controller, HDD and VGA enter the standby mode.

•

Stop the CPU internal clock.

•

All the functions are disabled except the keyboard, battery low warning and modem

ring wake up from standby (if enabled).

The condition back to

On Mode

Any one of following activities will let system back to Normal Mode:

•

Any keystroke (Internal KB or External KB)

•

Modem ring.

HIBERNATION MODE

In hibernation mode (also known as zero-volt hibernation-to-disk mode), power shuts off. The notebook

saves all system information onto the hard disk before it enters hibernation mode. Once you turn on the

power, the notebook restores this information and resumes where you left off upon leaving hibernation

mode.

Summary of Contents for Extensa 61X

Page 6: ...vi ...

Page 26: ...1 8 Service Guide Figure 1 5 Main Board Layout Bottom Side ...

Page 49: ...System Introduction 1 31 1 5 1 3 Power Management Figure 1 14 Power Management Block Diagram ...

Page 55: ...System Introduction 1 37 1 6 System Block Diagram Figure 1 15 System Block Diagram ...

Page 64: ...Major Chips Description 2 7 2 2 5 Pin Diagram Figure 2 4 M1521 Pin Diagram ...

Page 99: ...2 42 Service Guide 2 5 3 Pin Diagram Figure 2 10 C T 65550 Pin Diagram ...

Page 117: ...2 60 Service Guide Figure 2 12 Functional block diagram CardBus Card Interface ...

Page 119: ...2 62 Service Guide Figure 2 14 PCI to CardBus terminal assignments ...

Page 135: ...2 78 Service Guide 2 7 3 Pin Diagram Figure 2 16 NS87336VJG Pin Diagram ...

Page 145: ...2 88 Service Guide 2 8 2 Pin Diagram Figure 2 17 YMF715 Block Diagram ...

Page 185: ...Disassembly and Unit Replacement 4 5 Figure 4 3 Disassembly Sequence Flowchart ...

Page 209: ...B 2 Service Guide ...

Page 210: ...Exploded View Diagram B 3 ...