SERIES AP440 ACROPACK

USER

’S MANUAL

Acromag, Inc. Tel: 248-295-0310

- 23 - http://www.acromag.com

- 23 -

www.acromag.com

0x0000 001C

7:0

NOT USED

2

0x0000 0020

7:0

NOT USED

2

0x0000 0024

7:0

READ/WRITE – Port 7

Bank Status/Select Register

0x0000 0028→

0x00000040

31:0

NOT USED

2

Interrupt Enable Status Register (Read/Write) - (BAR0 + 0x0000 0000)

This read/write register is used to: enable board interrupt, and determine

the pending status of interrupts.

The function of each of the interrupt register bits are described in Table 3.6.

This register can be read or written with either 8-bit, 16-bit, or 32-bit data

transfers. A power-up or system reset sets all interrupt register bits to 0.

An enabled Event Sense bit and the board interrupt enabled when both

enabled will allow interrupts to be generated. Changing Debounce control

registers while interrupts are enabled can cause false interrupts. It is

recommended that interrupts be disabled prior to accessing Debounce

control registers.

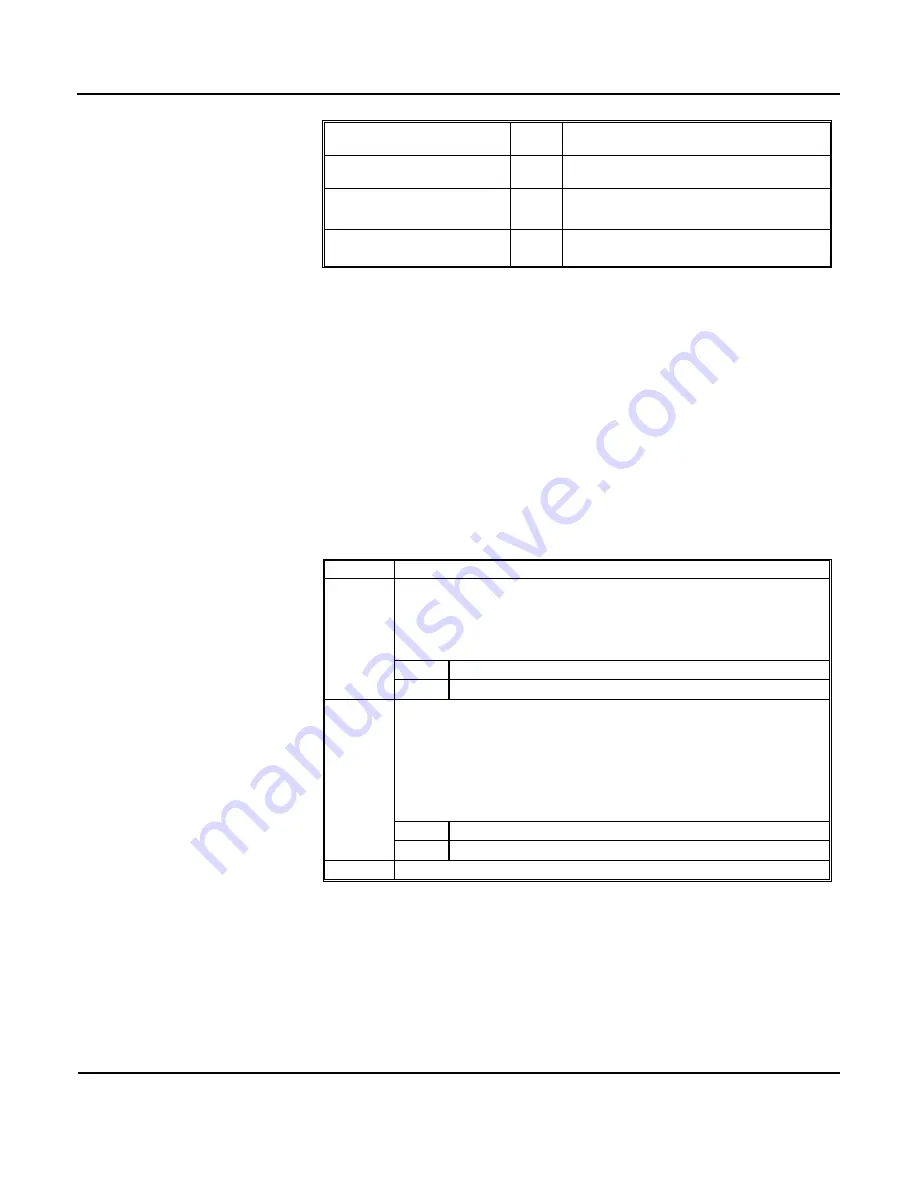

Table 3.7 Interrupt Register

Note that any registers/bits not

mentioned will remain at the

default value logic low.

Bit(s)

FUNCTION

0

Board Interrupt Enable Bit. This bit must be set to logic “1” to

enable generation of interrupts from the AP module. Setting

this bit to logic “0” will disable board interrupts. (Read/Write

Bit)

0

Disabled

1

Enabled

1

Interrupt Pending Status Bit. This bit can be read to

determine the interrupt pending status of the AP module.

When this bit is logic “1” an interrupt is pending and will cause

an interrupt request if bit-0 of the register is set. When this

bit is logic “0” an interrupt is not being requested.

0

No Interrupt

1

Interrupt Pending

31 to 2 Not Used