INDUSTRIAL I/O PACK SERIES APCe8650

PCI BUS CARRIER BOARD

Acromag, Inc. Tel: 248-295-0310

- 13 -

www.acromag.com

Configuration Transactions

The PCI bus is designed to recognize certain I/O accesses initiated by the host

processor as a configuration access. Configuration uses two 32-bit I/O ports

located at addresses 0CF8 and 0CFC hex. These two ports are:

32-bit configuration address port, occupying I/O addresses 0CF8 through 0CFB

hex.

32-bit configuration data port, occupying I/O addresses 0CFC through 0CFF

hex.

Configuration space, shown in Table 3-1,, is accessed by writing a 32-bit long-

word into the configuration address port that specifies the PCI bus, the carrier

board on the bus, and the configuration register on the carrier being

accessed. A read or write to the configuration data port will then cause the

configuration address value to be translated to the requested configuration

cycle on the PCI bus. Accesses to the configuration data port determine the

size of the access to the configuration register addressed and can be an 8, 16,

or 32-bit operation.

Any access to the Configuration address port that is not a 32-bit access is

treated like a normal computer I/O access. Thus, computer I/O devices using

8 or 16-bit registers are not affected because they will be accessed as

expected.

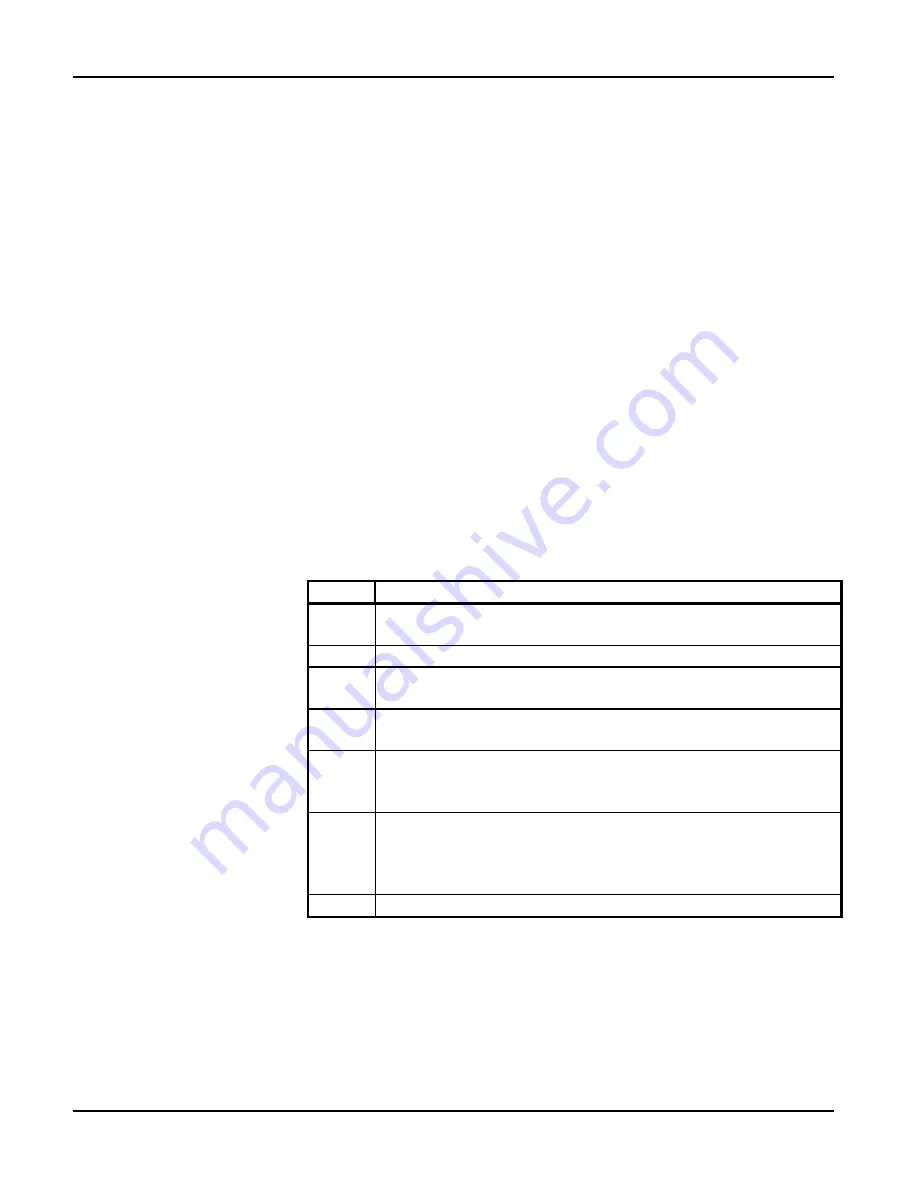

Table 3-1 Configuration Address Port

BIT

FUNCTION

31

Enables accesses to Configuration Data to be translated to

configuration cycles on the PCI bus.

30-24

Reserved, Return 0 when read.

23-16

Bus Number

Choose a specific PCI bus in the system. Zero if only one PCI bus.

15-11

Device Number

Choose a specific device/PCI board on the bus.

10-8

Function Number

Choose a specific function in a device. Function number is zero

for the APCe8650

7-2

Register Number

Used to indicate which PCI Configuration Register to access. The

Configuration Registers and their corresponding register numbers

are given in Table 3.2.

1-0

Read Only bits that return 0.

Configuration Registers

The PCI specification requires software driven initialization and configuration

via the Configuration Address space. This PCI carrier provides 256 bytes of

configuration registers for this purpose. The PCI carrier contains the

configuration registers, shown in Table 3-2, to facilitate Plug-and-Play

compatibility.