AXM-

A75 User’s Manual

Multifunction I/O Mezzanine Board

_____________________________________________________________________________________

- 22 -

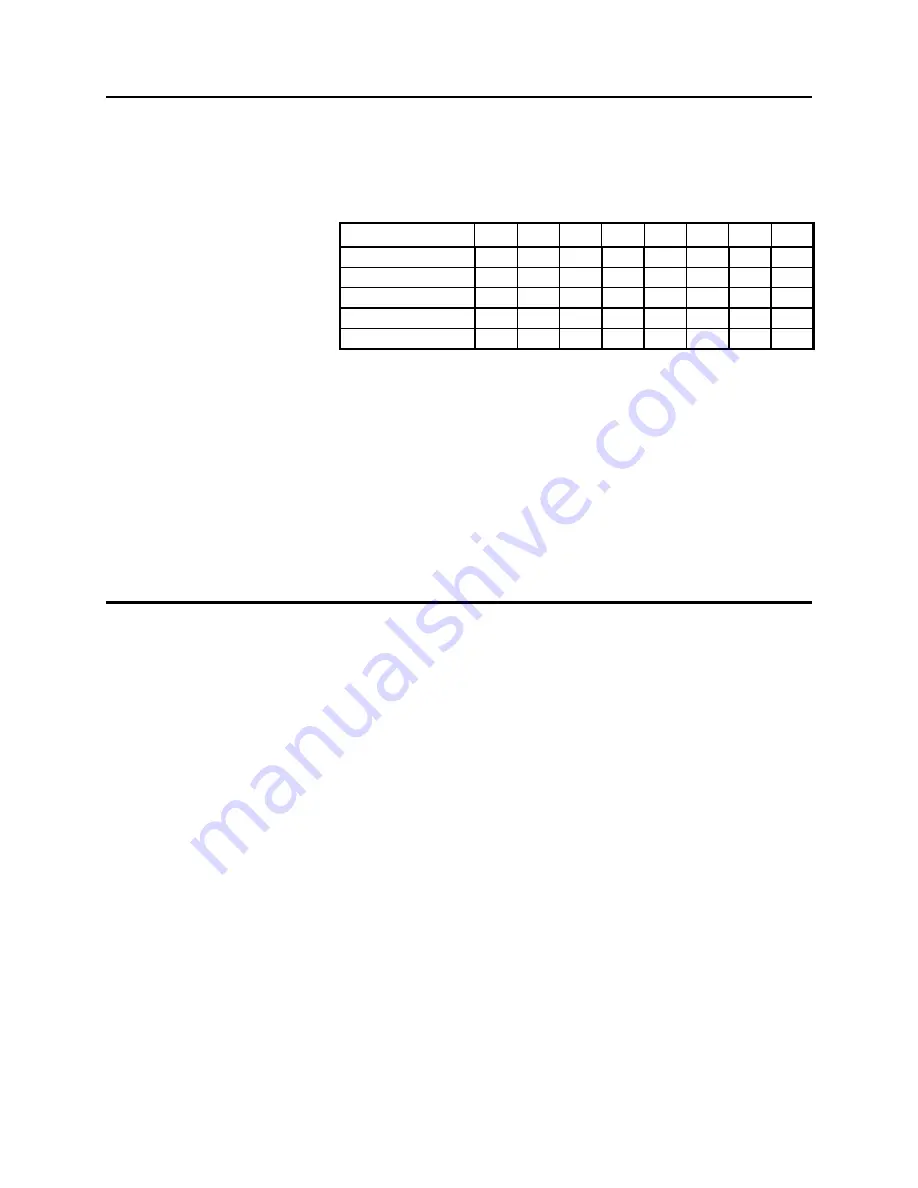

DAC Offset Register

The offset register is an eight bit register that allows the user to

adjust the offset of each DAC

by −

16 LSBs to +15.875 LSBs in steps of

one-eighth LSB, as shown in Table 3-17.

Table 3-17 DAC Offset Correction

Gain Adjustment

OF7 OF6 OF5 OF4 OF3 OF2 OF1 OF0

+15.875 LSBs

0

1

1

1

1

1

1

1

+15.75 LSBs

0

1

1

1

1

1

1

0

No adjustment

0

0

0

0

0

0

0

0

-15.875 LSBs

1

0

0

0

0

0

0

1

-16 LSBs

1

0

0

0

0

0

0

0

Note: the LDAC bit in the control register must be written to trigger a

transfer from the DAC data registers to the DAC offset register.

Updating DAC outputs

The values written to the DAC data registers are not immediately

applied to the DAC outputs. The LDAC bit in the control register must

be written to trigger a transfer from the DAC data registers to the

DAC outputs (see Table 3-4). The transfer from the data register to

DAC outputs occurs simultaneously for all DAC channels.

4.0

THEORY OF OPERATION

Field I/O Connections

The field I/O interface to the AXM-A75 is provided through connector P1 (refer to Table 2-1).

Field I/O

signals are NON-ISOLATED.

This means that the field return and logic common have a direct electrical

connection to each other. As such, care must be taken to avoid ground loops (see Section 2.0 for