SERIES IP1K110 INDUSTRIAL I/O PACK RECONFIGURABLE DIGITAL I/O MODULE

__________________________________________________________________________________________

- 16 -

Acromag, Inc. Tel:248-295-0310 Fax:248-624-9234 Email:solutions@acromag.com

http://www.acromag.com

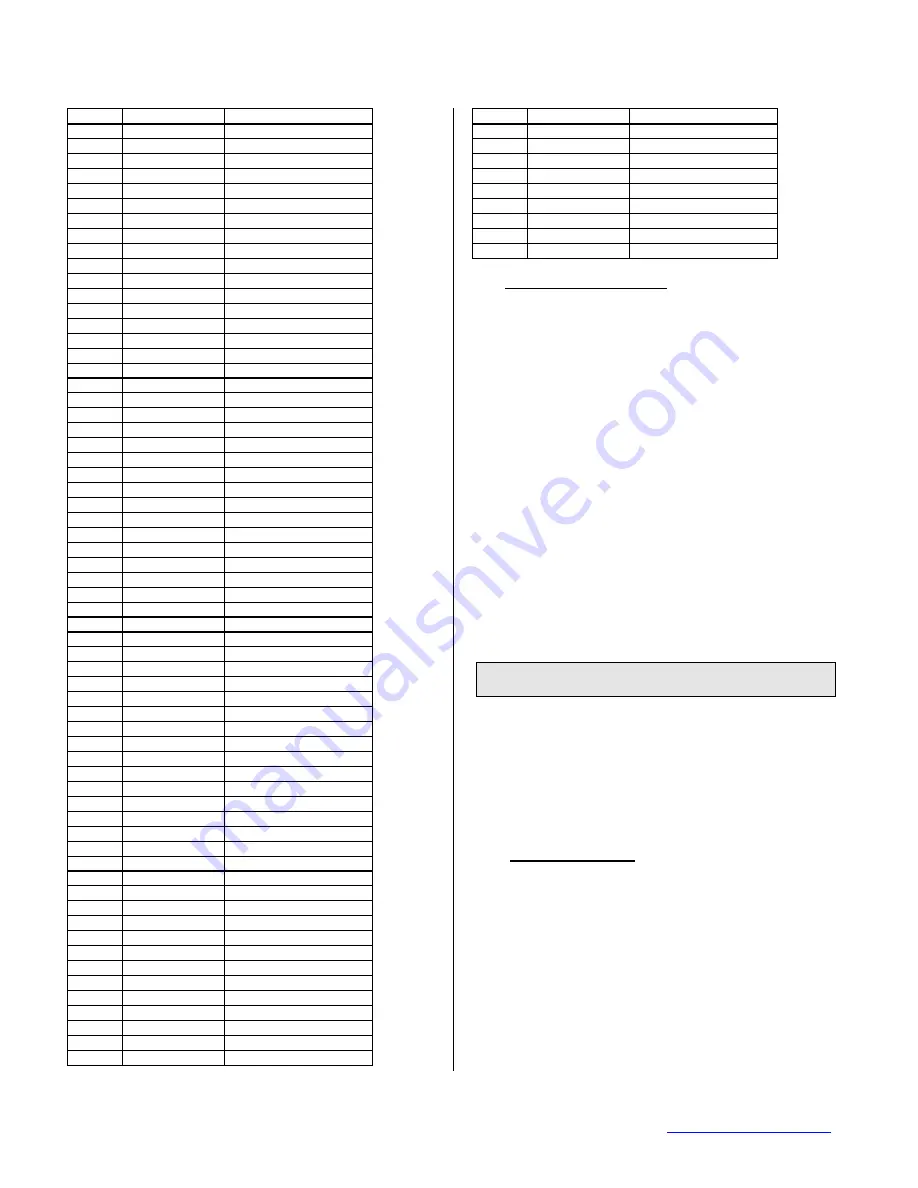

Pin

Signal

I/O

137

GND

GND

138

VCCIO

3.3Volts

139

DIFF_DIR3

Output (Pulled Low)

140

DIFF_DIR4

Output (Pulled Low)

141

DIFF_DIR5

Output (Pulled Low)

142

DIFF_DIR6

Output (Pulled Low)

143

DATA0

Bi-Dir D0 IP Bus

144

DATA8

Bi-Dir D8 IP Bus

145

GND

GND

146

VCCIO

3.3Volts

147

DATA9

Bi-Dir D9 IP Bus

148

DATA10

Bi-Dir D10 IP Bus

149

DATA11

Bi-Dir D11 IP Bus

150

DATA12

Bi-Dir D12 IP Bus

151

GND

GND

152

VCCINT

2.5Volts

153

TDI

(Pulled High)

154

nCE

Input (Tied Low)

155

DCLK

Input (Pulled High)

156

DATA0

PD00 From CPLD

157

DATA1

Bi-Dir D1 IP Bus

158

DATA2

Bi-Dir D2 IP Bus

159

DATA3

Bi-Dir D3 IP Bus

160

DATA13

Bi-Dir D13 IP Bus

161

DATA4

Bi-Dir D4 IP Bus

162

DATA5

Bi-Dir D5 IP Bus

163

DATA14

Bi-Dir D14 IP Bus

164

DATA6

Bi-Dir D6 IP Bus

165

VCCIO

3.3Volts

166

DATA7

Bi-Dir D7 IP Bus

167

DATA15

Bi-Dir D15 IP Bus

168

Config_Enable

Output (Pulled High)

169

Ref Clock

Output CY22150 ref clk

170

IP Reset

Input

171

GND

GND

172

A1

Input IP Bus

173

A2

Input IP Bus

174

A3

Input IP Bus

175

A4

Input IP Bus

176

A5

Input IP Bus

177

A6

Input IP Bus

178

VCCIO

3.3Volts

179

nIOsel

Input IP Bus

180

nIDsel

Input IP Bus

181

GND

GND

182

nMEMsel

Input IP Bus

183

Gen Clock

Input Generated Clk

184

nINTsel

Input IP Bus

185

VCCINT

2.5Volts

186

R_nW

Input IP Bus

187

nAck

Output IP Bus

188

GND

GND

189

nIntReq0

Output IP Bus

190

nIntReq1

Output IP Bus

191

nDMAReq0

Output IP Bus

192

nDMAReq1

Output IP Bus

193

nDMAck

Input IP Bus

194

VCCIO

3.3Volts

195

nDMAend

Bi-Dir IP Bus

196

nStrobe

Bi-Dir IP Bus

197

SCLK

Output CY22150 Clk

198

SDATA

Output CY22150 Data

199

TTL_DIR6

Output (Pulled High)

Pin

Signal

I/O

200

TTL_DIR5

Output (Pulled High)

201

VCCINT

2.5Volts

202

TTL_DIR4

Output (Pulled High)

203

TTL_DIR3

Output (Pulled High)

204

TTL_DIR1

Output (Pulled High)

205

TTL_DIR2

Output (Pulled High)

206

nWS

Input (From CPLD)

207

CS

Input (From CPLD)

208

nCS

Input (From CPLD)

5.0 SERVICE AND REPAIR

SERVICE AND REPAIR ASSISTANCE

Surface-Mounted Technology (SMT) boards are generally

difficult to repair. It is highly recommended that a non-functioning

board be returned to Acromag for repair. The board can be easily

damaged unless special SMT repair and service tools are used.

Further, Acromag has automated test equipment that thoroughly

checks the performance of each board. When a board is first

produced and when any repair is made, it is tested, placed in a

burn-in room at elevated temperature, and retested before

shipment.

Please refer to Acromag's Service Policy Bulletin or contact

Acromag for complete details on how to obtain parts and repair.

PRELIMINARY SERVICE PROCEDURE

Before beginning repair, be sure that all of the procedures in

Section 2, Preparation For Use, have been followed. Also, refer

to the documentation of your carrier board to verify that it is

correctly configured. Replacement of the module with one that is

known to work correctly is a good technique to isolate a faulty

module.

CAUTION:

POWER MUST BE TURNED OFF BEFORE

REMOVING OR INSERTING BOARDS

Initial testing and use of the IP1K110 should be

implemented with the Acromag supplied FPGA configuration

file. This will allow one to verify the correct operation of the

IP1K110 hardware.

Acromag’s Applications Engineers can provide further

technical assistance if required. When needed, complete repair

services are also available from Acromag.

6.0 SPECIFICATIONS

PHISICAL

Physical Configuration.............. Single Industrial Pack Module.

Length................................ 3.880 in. (98.5 mm).

Width.................................. 1.780 in. (45.2 mm).

Board Thickness.................0.062 in. (1.59 mm).

Max Component Height...... 0.290 in. (7.37 mm).

Connectors:

P1 (IP Logic Interface)........ 50-pin female receptacle header

(AMP 173279-3 or equivalent).

P2 (Field I/O)...................... 50-pin female receptacle header

(AMP 173279-3 or equivalent).