SERIES IP1K110 INDUSTRIAL I/O PACK RECONFIGURABLE DIGITAL I/O MODULE

__________________________________________________________________________________________

- 17 -

Acromag, Inc. Tel:248-295-0310 Fax:248-624-9234 Email:solutions@acromag.com

http://www.acromag.com

Power:

+5 Volts (

±

5%)..............….. 410mA, Typical for Acromag

configuration file.

480mA Maximum.

+/-12 Volts (

±

5%) from P1.. 0mA (Not Used)

Maximum Vcc Rise Time.... 100m seconds

ENVIRONMENTAL

Operating Temperature.........… Standard Unit 0 to +70

°

C.

E Version -40 to 85

°

C.

Relative Humidity...................... 5-95% Non-Condensing.

Storage Temperature................ -55

°

C to +125

°

C.

Non-Isolated............................. Logic and field commons have a

direct electrical connection.

Resistance to RFI..................... Complies with IEC1000-4-3 (3

V/m, 80 to 1000MHz AM &

900MHz. Keyed) and European

Norm EN50082-1 with no digital

upsets.

Electromagnetic Interference

Immunity (EMI).........................

No register upsets under the

influence of EMI from switching

solenoids, commutator motors,

and drill motors.

Surge Immunity.....................… Not required for signal I/O per

European Norm EN50082-1.

Electric Fast Transient

Immunity EFT...........................

Complies with IEC1000-4-4 Level

2 (0.5KV at field input and output

terminals) and European Norm

EN50082-1.

Radiated Emissions. ................ Meets or exceeds European

Norm EN50081-1 for class A

equipment.

Warning: This is a class A product. In a domestic environment

this product may cause radio interference in which the

user may be required to take adequate measures.

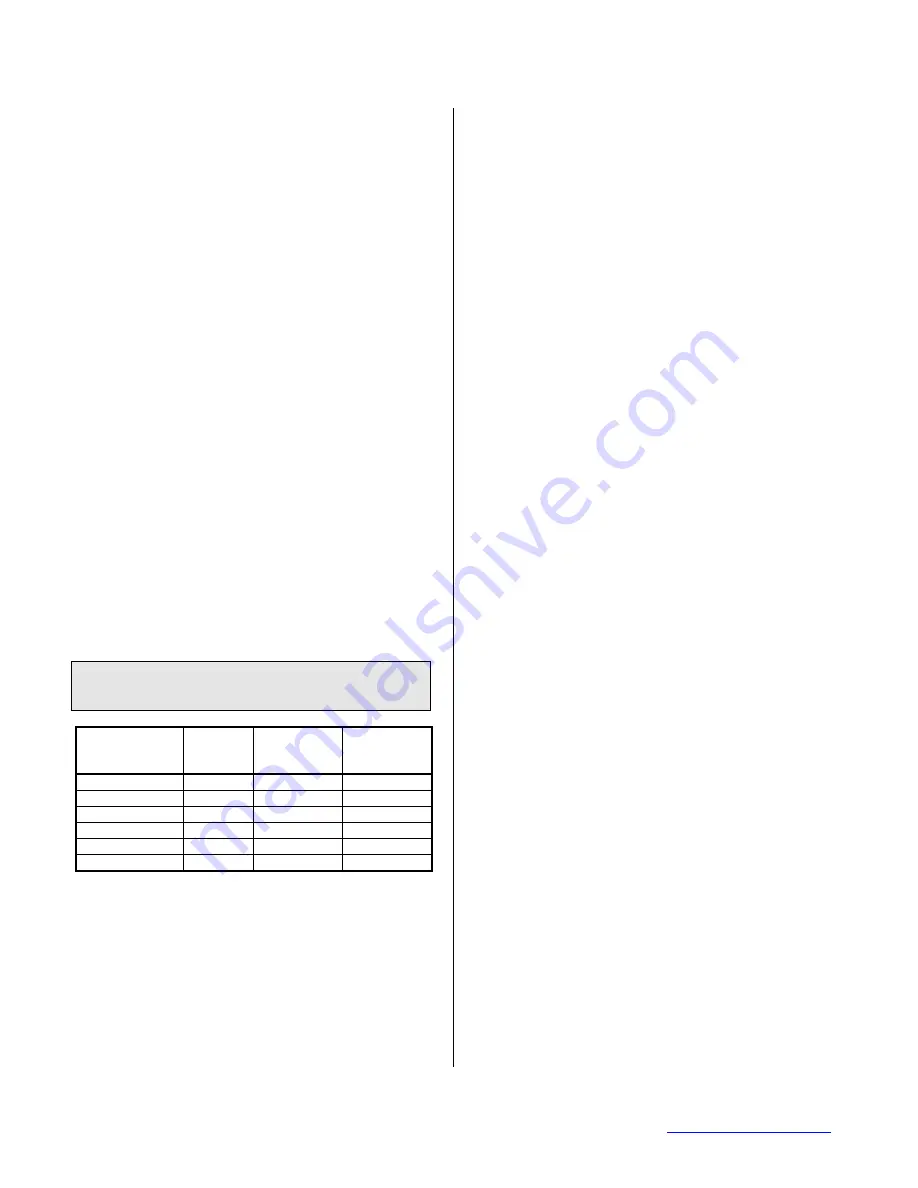

Model

TTL

Channels

EIA-485/422

Channels

Operating

Temperature

Range

IP1K110-0024

0

24

0 to 70°C

IP1K110-2412

24

12

0 to 70°C

IP1K110-4800

48

0

0 to 70°C

IP1K110-0024E

0

24

-40 to 85°C

IP1K110-2412E

24

12

-40 to 85°C

IP1K110-4800E

48

0

-40 to 85°C

EIA-RS485 TRANSCEIVERS

Channel Configuration.............. Up to 24, non-isolated EIA

RS485/RS422 serial ports with a

common signal return

connection. Selected in blocks of

4 signal pairs/channels when

ordered.

Data Rate................................. 30M bits/sec, Maximum.

Cable Length............................ 4000 feet, Maximum. Use of a

signal repeater can extend

transmission distances beyond

this limit.

Termination Resistors............... Termination Resistors are not

provided. Termination resistors

are recommended at network

end points only (see Drawing

4501-702 for location).

Differential Output Voltage........ 5V Maximum; 1.5V Minimum

(with 27

Ω

load).

Common Mode Output

Voltage.....................................

3V Maximum.

Output Short Circuit Current......250mA, Maximum.

Input Hysteresis........................ 70mV (V

CM

=0V).

TTL TRANSCEIVERS

Channel Configuration.............. Up to 48, non-isolated TTL

signals. Selected in blocks of 8

channels when ordered.

Integrated Circuit Device

Pericom PI74FCT623T

http://www.pericom.com/

INDUSTRIAL I/O PACK COMPLIANCE

Specification............................. This device meets or exceeds all

written Industrial I/O Pack

specifications per ANSI/VITA 4

1995 for 8MHz or 32MHz

operation for Type I Modules.

Electrical/Mechanical

Interface...................................

Single-Size IP Module.

I/O Space................................. 16-bit and 8-bit:

ID Space...................................16 and 8-bit; Supports Type 1, 32

bytes per IP (consecutive odd

byte addresses). IPAH is used to

indicate 32MHz operation (8MHz

operation is also supported).

Memory Space......................... Supported by hardware but not

implemented in example design.

Interrupts................................. Generates INTREQ0

∗

interrupt

request per IP and interrupt

acknowledge cycles via access

to IP INT space.

INTREQ1

∗

available but not

driven by example FPGA design.

DMA......................................... Two IP request levels available

but not implemented in example

FPGA design.

Interrupts:

Handling Format....................... An 8-bit vector is provided during

interrupt acknowledge cycles on

data lines D0…D7. The release

mechanism is RORA type

(Release On Register Access).

FPGA

FPGA....................................... Altera EP1K100QC208-1

100K typical gates and 49,152

RAM bits