SERIES IP1K110 INDUSTRIAL I/O PACK RECONFIGURABLE DIGITAL I/O MODULE

__________________________________________________________________________________________

- 5 -

Acromag, Inc. Tel:248-295-0310 Fax:248-624-9234 Email:solutions@acromag.com

http://www.acromag.com

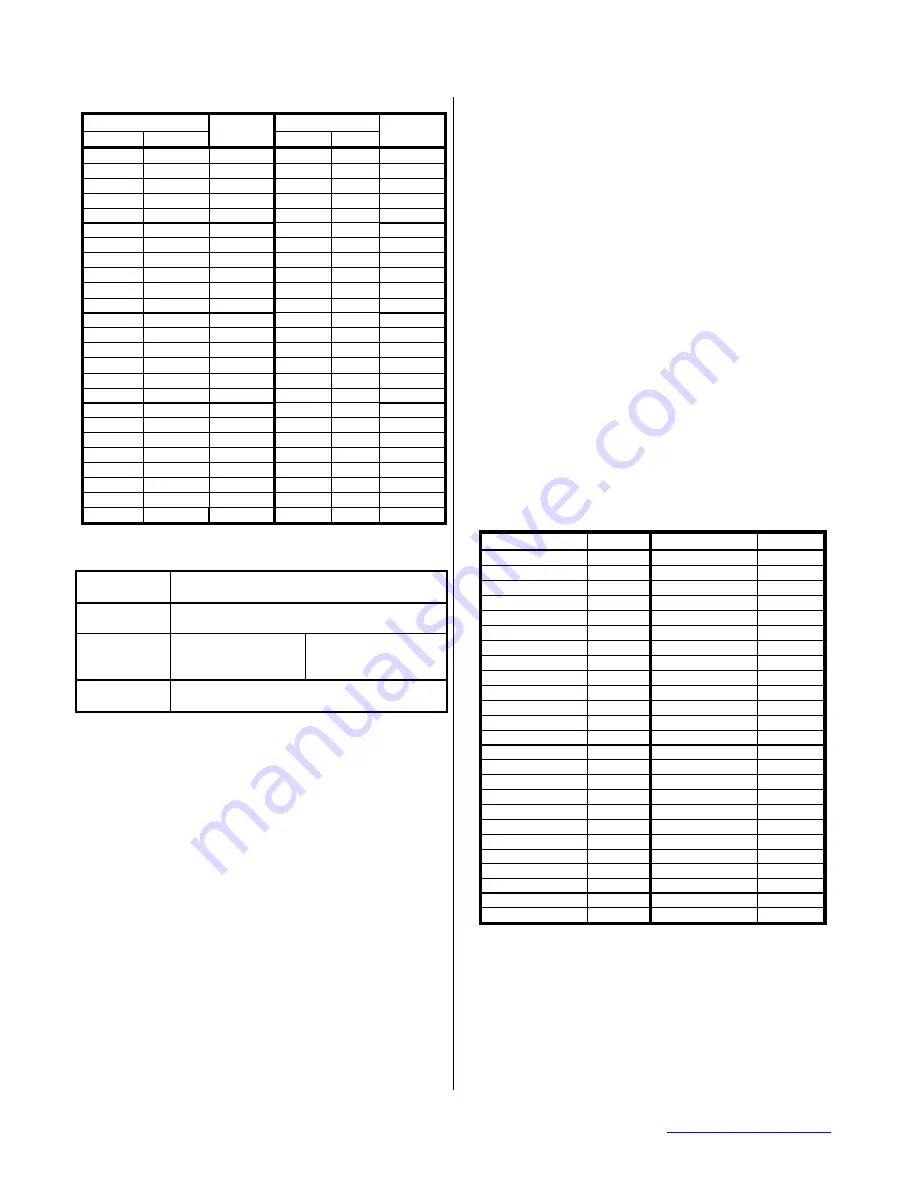

Table 2.1: IP1K110 Field I/O Pin Connections (P2)

Pin Description

Pin

Number

Pin Description

Pin

Number

RS485

TTL

RS485

TTL

I/O00+

I/O00

1

I/O12-

I/O25

26

I/O00-

I/O01

2

I/O13+

I/O26

27

I/O01+

I/O02

3

I/O13-

I/O27

28

I/O01-

I/O03

4

I/O14+

I/O28

29

I/O02+

I/O04

5

I/O14-

I/O29

30

I/O02-

I/O05

6

I/O15+

I/O30

31

I/O03+

I/O06

7

I/O15-

I/O31

32

I/O03-

I/O07

8

I/O16+

I/O32

33

I/O04+

I/O08

9

I/O16-

I/O33

34

I/O04-

I/O09

10

I/O17+

I/O34

35

I/O05+

I/O10

11

I/O17-

I/O35

36

I/O05-

I/O11

12

I/O18+

I/O36

37

I/O06+

I/O12

13

I/O18-

I/O37

38

I/O06-

I/O13

14

I/O19+

I/O38

39

I/O07+

I/O14

15

I/O19-

I/O39

40

I/O07-

I/O15

16

I/O20+

I/O40

41

I/O08+

I/O16

17

I/O20-

I/O41

42

I/O08-

I/O17

18

I/O21+

I/O42

43

I/O09+

I/O18

19

I/O21-

I/O43

44

I/O09-

I/O19

20

I/O22+

I/O44

45

I/O10+

I/O20

21

I/O22-

I/O45

46

I/O10-

I/O21

22

I/O23+

I/O46

47

I/O11+

I/O22

23

I/O23-

I/O47

48

I/O11-

I/O23

24

NC

NC

49

I/O12+

I/O24

25

GND

GND

50

Table 2.2: IP1K110 Model Channel Assignments

Model

I/O Register Bits

See Table 2.1 for Pin Assignments

IP1K110-0024

Differential/RS485 Channels

±

0 to

±

23

IP1K110-2412

Differential /RS485

Channels

±

12 to

±

23

TTL Channels

0 to 23

IP1K110-4800

TTL Channels 0 to 47

I/O Noise and Grounding Considerations

The IP1K110 is non-isolated between the logic and field I/O

grounds since output common is electrically connected to the IP

module ground. Consequently, the field I/O connections are not

isolated from the carrier board and backplane. Two ounce

copper ground plane foil has been employed in the design of this

model to help minimize the effects of ground bounce, impedance

drops, and switching transients. However, care should be taken

in designing installations without isolation to avoid noise pickup

and ground loops caused by multiple ground connections.

To minimize high levels of EMI the signal ground connection

at the field I/O port (pin 50) should be used to provide a path for

induced common-mode noise and currents. The ground path

provides a low-impedance path to reduce emissions.

EIA RS485/RS422 communication distances are generally

limited to less than 4000 feet. To minimize transmission-line

problems, all nodes connected to the cable must use minimum

stub length connections. The optimal configuration for the

RS485/RS422 bus is a daisy-chain connection from node 1 to

node 2 to node 3 to node n. The bus must form a single

continuous path, and the nodes in the middle of the bus must not

be at the ends of long branches, spokes, or stubs. See Drawing

4501-702 for example connection and termination practices.

Transmission line signal reflections can be minimized with

proper termination. The EIA RS485/RS422 standard allows up to

32 driver/receivers to be connected to a single bus. Termination

resistors should only be used at the two extreme ends of the bus

and not at each of the nodes of the bus. Termination resistors

are not provided on the IP1K110. They can be added to the field

wiring as near to the IP module as possible.

IP Logic Interface Connector (P1)

P1 of the IP module provides the logic interface to the mating

connector on the carrier board. This connector is a 50-pin female

receptacle header (AMP 173279-3 or equivalent) which mates to

the male connector of the carrier board (AMP 173280-3 or

equivalent). This provides excellent connection integrity and

utilizes gold-plating in the mating area. Threaded metric M2

screws and spacers are supplied with the IP module to provide

additional stability for harsh environments (see Drawing 4501-434

for assembly details). Field and logic side connectors are keyed

to avoid incorrect assembly. The pin assignments of P1 are

standard for all IP modules according to the Industrial I/O Pack

Specification (see Table 2.3). Note that the IP1K110 does not

utilize all of the logic signals defined for the P1 connector and

these are indicated in

BOLD ITALICS

.

Table 2.3: Standard Logic Interface Connections (P1)

Pin Description

Number

Pin Description

Number

GND

1

GND

26

CLK

2

+5V

27

Reset

∗

3

R/W

∗

28

D00

4

IDSEL

∗

29

D01

5

DMAReq0

∗

30

D02

6

MEMSEL

∗

31

D03

7

DMAReq1

∗

32

D04

8

IntSel

∗

33

D05

9

DMAck0

∗

34

D06

10

IOSEL

∗

35

D07

11

RESERVED

36

D08

12

A1

37

D09

13

DMAEnd

∗

38

D10

14

A2

39

D11

15

ERROR

∗

40

D12

16

A3

41

D13

17

INTReq0

∗

42

D14

18

A4

43

D15

19

INTReq1

∗

44

BS0

∗

20

A5

45

BS1

∗

21

STROBE

∗

46

-12V

22

A6

47

+12V

23

ACK

∗

48

+5V

24

RESERVED

49

GND

25

GND

50

Asterisk (*) is used to indicate an active-low signal.

BOLD ITALIC

Logic Lines are NOT USED by this IP Model.