A

I

_

a

•

•

•

•

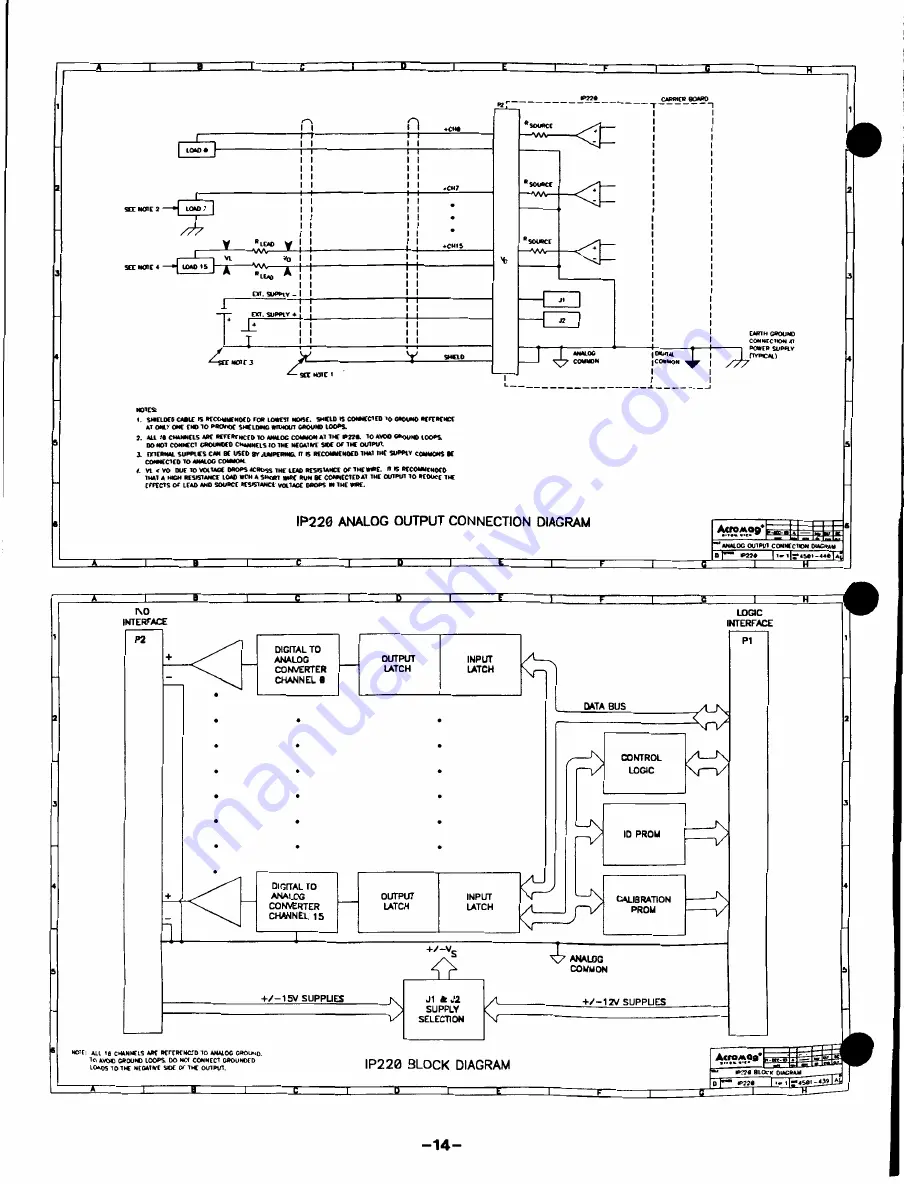

DATA BUS

CONTROL

LOGIC

ID PROM

DIGITAL TO

ANALOG

OUTPUT

INPUT

CALIBRATION

CONVERTER

LATCH

LATCH

PROM

CHANNEL 15

1

G

I

F

I

G

2

3

4

A

P2

n

•CTIR

LOM) •

C*17

SEE NOTE 2 L O W 7

/ 7 1 7

SEE NOTE 4

C1115

LOAD 15

VL

Y

o

'LEAD

DO. SUPPLY -

T

D

a

.

SuppLV •

t o t N o r

sr NOTE

Noi

r I

W E L 0

NOIES

1. W E L D E D CABLE .5 RECOMMENOED TOR LOWEST 10151. SNELD IS CONNECTED 10 GRouNo . 5 r r m o c r

AT ONLY OW CND 10 PROTOC S.ELDING1KINCUT MOUND LOOPS

7. ALL 14 CNOINELS ARE REVERENCED 10 ANALOG C05114011 AllNE IP724. 1 0 m o o G i s m o w o n

Do POT CONNECT GROUNDED CIMPINELS TO 'ME NECATNE SO( Of THE OUTPUT.

ETTEINIAL SUPPLIES C441 BE USED PrJUMPERING IT IS RECOMMENDED THAT 114E SUPPLY COMMONS SC

c o o c r o c o 10 NOLOG COMMON.

4. V t

A VO DUE TO VOLTAGE DROPS ACROSS NNE LEAD 11151510CE

Or NNE WOE

R Is o c o c o m o o t o

TNAT A NON RESISTN4CE LON:1*nm A SNORT I N K RUN BE CONNECTED Al I I I OUTPUT 10 *COLIC( LIE

r o c o s Or LEAD AND SOURCE rorsoomcc m u m DROPS N I N E

1P2241

CARRIER c o o p

*soma'

V.15

•

•

21

J7

-

N

7

ANALOG

COMMON

IP220 ANALOG OUTPUT CONNECTION DIAGRAM

WAAL

COMMON

(ARM GROUND

CC•ANECL.044 Al

4014E1. SVOOLv

(TvINCAL)

Aoromog•

-

w

P t

""APOLOG OUTPUT CC.N(C112.1 DIAGRAM

D T " P 2 2 4 1 1 , 7 4 5 4 0 - 4 4 6 1 4

C_

1

2

4

5

INTERFACE

P2

DIGITAL TO

ANALOG

CONVERTER

CHANNEL •

OUTPUT

LATCH

INPUT

LATCH

1

LOGIC

INTERFACE

+ / - 1 5 v suPPUES

ALL l e ColkilliWLS

A M

REVERENCED To ANALOG GROUND.

10 AVOID Gnome rooPs. DO NOT CONNECT GROUNDED

LOADS TO THE NEGATNE SOC o r TIE OUTPUT.

+/—v

JI & J 2

SUPPLY

SELECTION

Z , ANALOG

COMMON

+ / - 1 2 v SUPPLIES

IP220 BLOCK DIAGRAM

P1

0221

OLccv DIAGRAM

.44501 -439

14221

I

i •

A

- 1 4 -