IP482 Industrial I/O Pack User’s Manual Counter Timer Module

___________________________________________________________________

________________________________________________________________________________________

Acromag, Inc. Tel:248-295-0310 Fax:248-624-9234 Email:solutions@acromag.com http://www.acromag.com

15

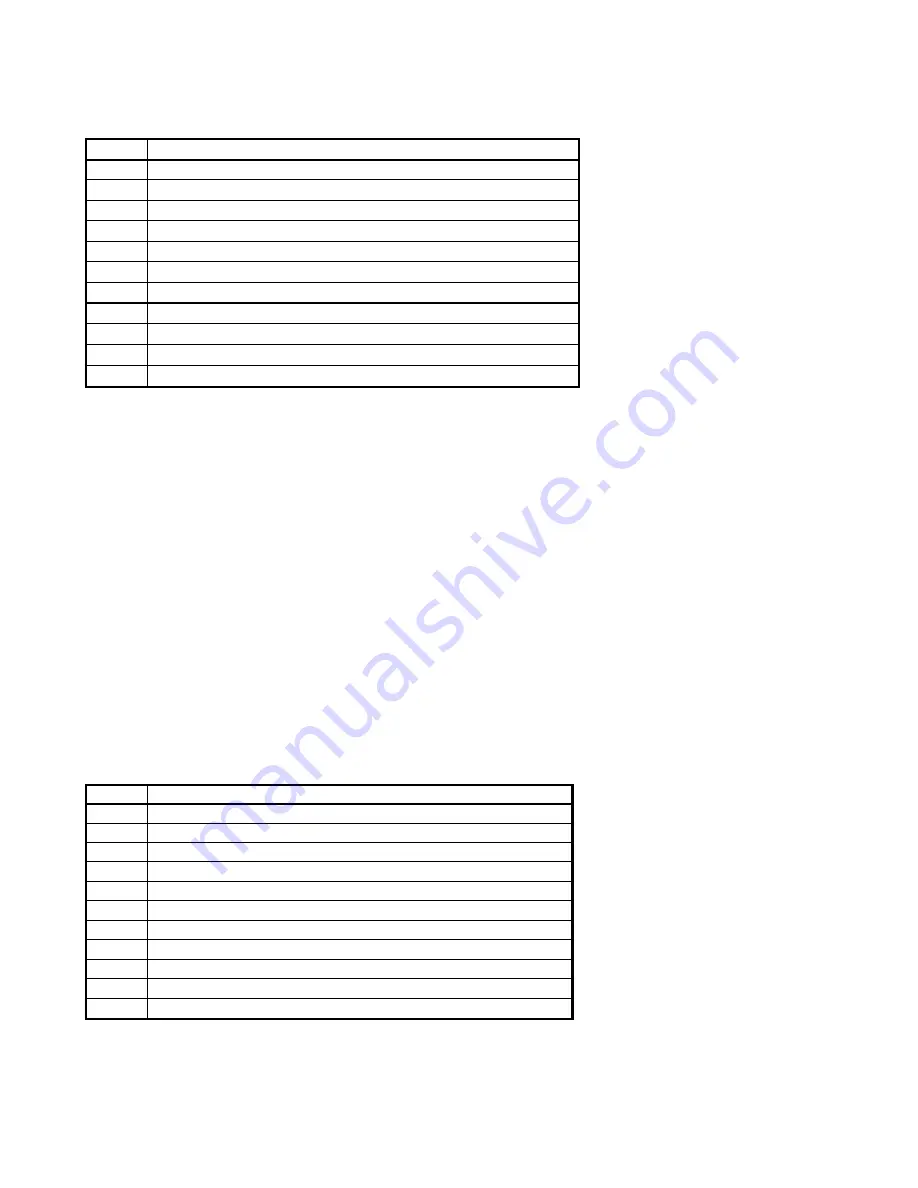

BIT

FUNCTION

0

Counter/Timer 1 Interrupt Pending/Clear

1

Counter/Timer 2 Interrupt Pending/Clear

2

Counter/Timer 3 Interrupt Pending/Clear

3

Counter/Timer 4 Interrupt Pending/Clear

4

Counter/Timer 5 Interrupt Pending/Clear

5

Counter/Timer 6 Interrupt Pending/Clear

6

Counter/Timer 7 Interrupt Pending/Clear

7

Counter/Timer 8 Interrupt Pending/Clear

8

Counter/Timer 9 Interrupt Pending/Clear

9

Counter/Timer 10 Interrupt Pending/Clear

10-15

Not Used

1

A Counter/Timer that is not interrupt enabled will never set its interrupt

status flag. A Counter/Timer interrupt can be cleared by writing a “1” to its

bit position in the Interrupt Status/Clear Register (writing a “1” acts as a

reset signal to clear the set state). The interrupt will be generated again, if

the condi

tion which caused the interrupt to occur remains. Writing “0” to a

bit location has no effect. That is, a pending interrupt will remain pending.

Writing to this register is possible via 16-bit or 8-bit data transfers.

A power-up or system reset clears all interrupts, setting all bits in the

Interrupt Status/Clear Register to logic “0”.

Counter Trigger Register (Write) - (Base + 04H)

This register is used to implement software triggering for all

counter/timers. Writing a 1 to the counter’s corresponding trigger bit of this

register will cause the counter function to be triggered. Table 3.5 identifies

the trigger bit location corresponding to each of the counters. The contents

of this register are not stored and merely act to trigger the corresponding

counters.

BIT

FUNCTION

0

Counter 1 Trigger

1

1

Counter 2 Trigger

1

2

Counter 3 Trigger

1

3

Counter 4 Trigger

1

4

Counter 5 Trigger

1

5

Counter 6 Trigger

1

6

Counter 7 Trigger

1

7

Counter 8 Trigger

1

8

Counter 9 Trigger

1

9

Counter 10 Trigger

1

10-15

Not Used

1

CONTROL REGISTERS

Table 3.4:

IP482

Counter/Timer Interrupt

Status/Clear

1. All bits labeled “Not Used”

will return logic “0” when read.

Table 3.5:

IP482 Counter

Trigger Register

1. All bits will return logic “0”

when read.