SERIES IP503 INDUSTRIAL I/O PACK EIA/TIA-232E & CENTRONICS COMMUNICATION MODULE

___________________________________________________________________________________________

- 19 -

THE CENTRONICS PARALLEL INTERFACE

This interface is a protocol for parallel data transfer first

developed by Centronics, a printer manufacturer. It has since

gained wide industry acceptance as an acceptable interface

between computers and printers

The parallel port signals can be divided into four groups:

control signals (four open-drain, TTL compatible output lines),

status signals (five TTL compatible input lines), data lines (eight

I/O lines), and ground (8 common lines)

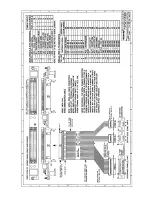

Pins 26-50 of the field I/O connector P2 provide connectivity

to the Centronics parallel port of this module (Refer to Table 21

for pin assignments)The functions of these pins are described in

the table below. Note that the pin numbers noted in the table

refer to the pin number of the common 25-pin “D” shell connector

used for parallel ports and not the P2 pin number (see Acromag

cable Model 5029-944)For P2 numbers, add 25 to the numbers

noted (refer to Table 21)

Centronics Parallel Port Signal Description

SIGNAL

DESCRIPTION

DATA (OUTPUT/INPUT)

PD0-PD7

(Pins 2-

9)

I/O, 8-bit Parallel Data Port Lines

CONTROL (OUTPUT/INPUT)

STB*

(Pin 1)

I/O, Open Drain, Line Printer Strobe - Active low

signal to the line printer to latch the data currently

on the parallel port. The output state of this line is

controlled via Bit 0 of the LPC control register. This

line is internally pulled up via 10K

Ω

AFD*

(Pin 14)

I/O, Open Drain, Line Printer AutoFeed - This

active low signal is sent to the printer when

continuous form paper is to be autofed to the

printer. When this signal is asserted low, the paper

is automatically fed 1 line after printing. This line is

internally pulled up via 10K

Ω

INIT*

(Pin 16)

I/O, Open Drain, Line Printer Initialize - This active

low signal triggers the start of the line printer

initialization routine. When this signal is asserted

low, the printer controller is reset to its power-up

state and the print buffer is cleared. This line is

internally pulled up via 10K

Ω

SLIN*

(Pin 17)

I/O, Open Drain, Line Printer Select - this active

low line selects the printer when asserted. Its

output state is controlled via Bit 3 of the LPC

control register. This line is internally pulled up via

10K

Ω

STATUS (INPUT)

ERR*

(Pin 15)

Input, Line Printer Error - This active low signal is

held low by the printer when an error condition

occurs at the printer This signal usually indicates

the printer is in a paper-end state, off-line state, or

other error state

SLCT

(Pin 13)

Input, Line Printer Select - this active high signal is

asserted by the line printer when it is selected. The

state of this line is monitored via Bit 4 of the LPS

status register

PE

(Pin 12)

Input, Line Printer Paper Empty - This active high

signal is asserted by the printer when it runs out of

paper

Centronics Parallel Port Signal Description continued

SIGNAL

DESCRIPTION

STATUS (INPUT)

BUSY

(Pin 11)

Input, Line Printer Busy - Active high signal from

the printer that is asserted when the printer is not

ready to accept more Data. The state of this bit is

monitored via Bit 7 of the LPS status register

ACKN*

(Pin 10)

Input, Line Printer Acknowledge - Active low signal

that indicates a successful data transfer has taken

place. Optionally, ACKN* can generate a printer

port interrupt during its positive transition. The

state of this line is monitored via Bit 6 of the LPS

status register

Pins 18-25 provide ground/shielding pins

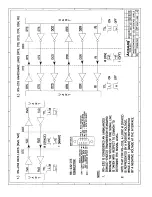

Like the RS-232 interface, the Centronics parallel interface

includes some lines that may or may not be supported by various

peripheral devices. However, the basic interface will include the

eight data lines (PD0-PD7) and three signal lines for handshaking

(Data Strobe*, Acknowledge*, and Busy)Data Strobe is an active

low signal line from the computer that indicates to the printer (or

other peripheral) that the data lines have valid information on

them. The trailing edge of Data Strobe causes the peripheral to

assert the active low ACKNowledge line. However, a busy

condition occurs when the printer is given a command to print the

line in the print buffer (carriage return), or when a vertical tab,

form feed, line feed, delete, bell, select, or deselect character is

sent. Receipt of one of these special characters causes the

printer to perform some related mechanical operation that

generally takes more than a few microseconds, causing the

handshake to change to busy condition timing and assert the

BUSY handshake line. That is, after the Data Strobe is negated,

BUSY is asserted instead of ACKNowledge, indicating that the

peripheral is busy and cannot complete the handshake for some

timeLater, after negating BUSY, the peripheral asserts

ACKNowledge for a few microseconds and busy-condition timing

ends with the negation of ACKNowledge

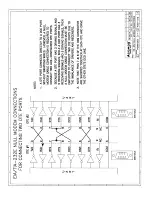

The Centronics interface of this module includes extended

mode support that allows the direction of data flow to be defined,

thus permitting two-way communication via the parallel

dataNormally the data lines are in the output mode, to put them

into the input mode, the port must be configured for extended

mode operation (see the LPC Register description)In extended

mode, data lines can be programmed for input or output

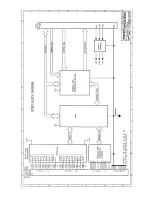

IP503 OPERATION

Connection to both serial ports and the parallel port is

provided through connector P2 (refer to Table 21)These serial

port pins are tied to the inputs and outputs of EIA/TIA-232E line

receivers and drivers. The function of the line receivers are to

convert the required EIA/TIA-232E signals to the TTL levels

required by the UART (Universal Asynchronous

Receiver/Transmitter)The line drivers convert the UART TTL

levels to the EIA/TIA-232E voltage levels. The UART provides

the necessary conversion from serial-to-parallel (receive) and

parallel-to-serial (transmit) for interfacing to the data bus.

Additionally, it provides data buffering and data formatting

capabilities, as well as a Centronics parallel interfAce. A

programmable logic device is used to control the interface

between the UART, the IP bus, and the serial line drivers and

receivers