SERIES IP503 INDUSTRIAL I/O PACK EIA/TIA-232E & CENTRONICS COMMUNICATION MODULE

___________________________________________________________________________________________

- 4 -

This board is physically protected with

packing material and electrically

protected with an anti-static bag during

shipment. However, it is

recommended that the board be

visually inspected for evidence of

mishandling prior to applying power

The board utilizes static-sensitive

components and should only be

handled at a static-safe workstation

CARD CAGE CONSIDERATIONS

Refer to the specifications for loading and power

requirements Be sure that the system power supplies are able to

accommodate the power requirements of the carrier board, plus

the installed IP modules, within the voltage tolerances specified

IMPORTANT: Adequate air circulation must be provided to

prevent a temperature rise above the maximum operating

temperature

The dense packing of the IP modules to the carrier board

restricts air flow within the card cage and is cause for concern

Adequate air circulation must be provided to prevent a

temperature rise above the maximum operating temperature and

to prolong the life of the electronics. If the installation is in an

industrial environment and the board is exposed to environmental

air, careful consideration should be given to air-filtering

BOARD CONFIGURATION

Power should be removed from the board when installing IP

modules, cables, termination panels, and field wiring. Refer to

Mechanical Assembly Drawing 4501-434 and your IP module

documentation for configuration and assembly instructions.

Model IP503 communication boards have no hardware jumpers

or switches to configure

CONNECTORS

IP Field I/O Connector (P2)

P2 provides the field I/O interface connections for mating IP

modules to the carrier boardP2 is a 50-pin female receptacle

header (AMP 173279-3 or equivalent) which mates to the male

connector of the carrier board (AMP 173280-3 or equivalent)This

provides excellent connection integrity and utilizes gold-plating in

the mating area. Threaded metric M2 screws and spacers are

supplied with the module to provide additional stability for harsh

environments (see Mechanical Assembly Drawing 4501-434)The

field and logic side connectors are keyed to avoid incorrect

assemblyP2 pin assignments are unique to each IP model (see

Table 21) and normally correspond to the pin numbers of the field

I/O interface connector on the carrier board (you should verify this

for your carrier board)An optional interface cable (Model 5029-

944) is available to convert the field I/O connector to common

DB9 (serial port) and DB25 (parallel port) port connectors

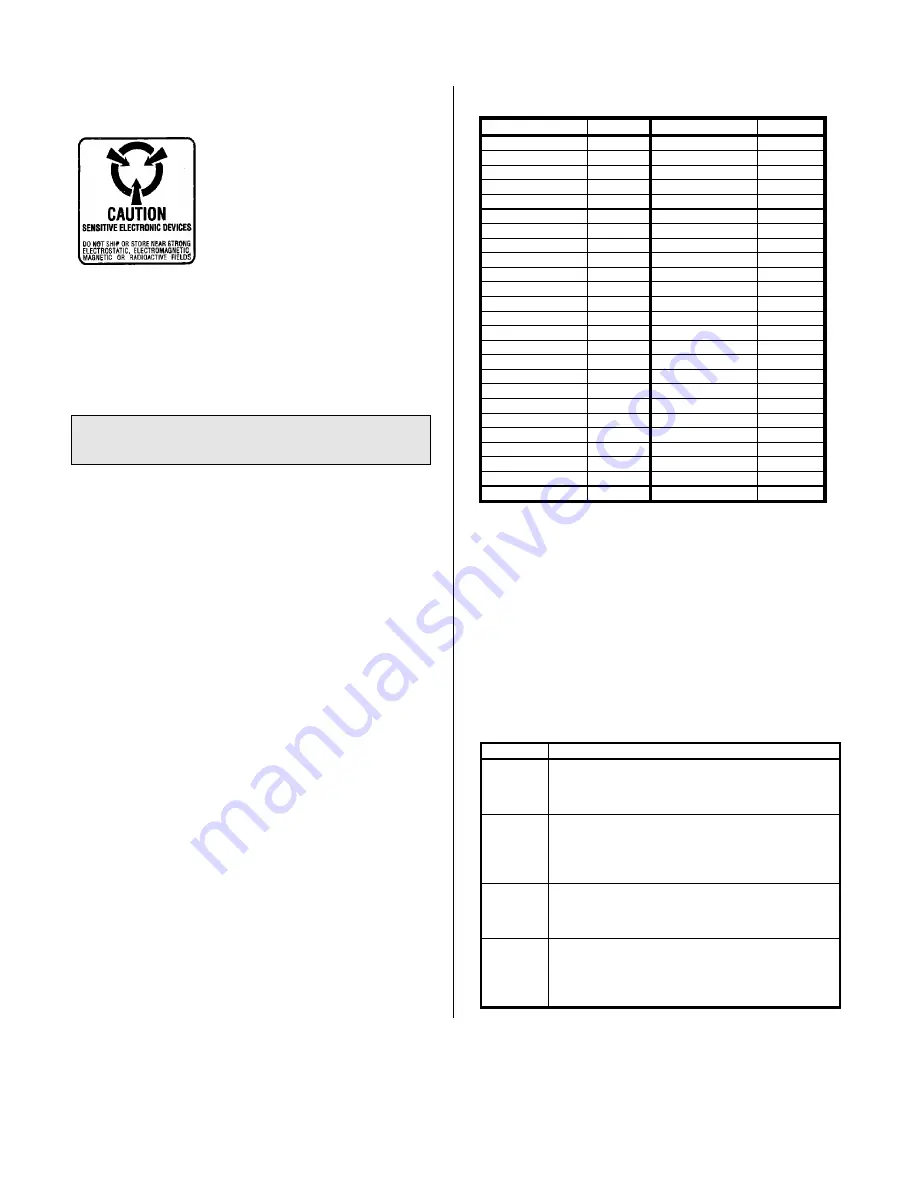

Table 21:IP503 Field I/O Pin Connections (P2)

Pin Description

Number

Pin Description

Number

COMMON

1

STB*

26

RI_A*

2

AFD*

27

DTR_A*

3

PD0

28

CTS_A*

4

ERR*

29

TXD_A

5

PD1

30

RTS_A*

6

INIT*

31

RXD_A

7

PD2

32

DSR_A*

8

SLIN*

33

DCD_A*

9

PD3

34

COMMON

10

COMMON

35

RI_B*

11

PD4

36

DTR_B*

12

COMMON

37

CTS_B*

13

PD5

38

TXD_B

14

COMMON

39

RTS_B*

15

PD6

40

RXD_B

16

COMMON

41

DSR_B*

17

PD7

42

DCD_B*

18

COMMON

43

COMMON

19

ACKN*

44

COMMON

20

COMMON

45

COMMON

21

BUSY

46

COMMON

22

COMMON

47

COMMON

23

PE

48

COMMON

24

COMMON

49

COMMON

25

SLCT

50

An Asterisk (*) is used to indicate an active-low signal

Note that the pin-wire assignments are arranged such that

IDC D-SUB ribbon cable connectors can be conveniently

attached to provide serial port A (pins 1-9), serial port B (pins 10-

18), & Centronics port (pins 26-50) connectivity (see Acromag

cable Model 5029-944)In Table 21, a suffix of “_A”, or “_B” is

appended to each pin label to denote its serial port association.

A brief description of each of the serial port signals at P2 is

included below. A complete functional description of all P2 pin

functions (including parallel port pins) is included in Section 40

(Theory Of Operation)Be careful not to confuse the A & B port

designations of the IP module with the IP carrier board A & B slot

designations

P2 Pin Signal Descriptions

SIGNAL

DESCRIPTION

DCD_A*

DCD_B*

Data Carrier Detect - An active low signal that

indicates the carrier has been detected by the

modem. The status of this signal is read via bit 7

of the Modem Status Register

DSR_A*

DSR_B*

Data Set Ready- A modem status signal to indicate

that it is connected to the line (it has no effect on

the transmit or receive operation)The status of this

signal is read via bit 5 of the Modem Status

Register

RxD_A

RxD_B

Receive Data Line Input - This is the receive data

input line. During Loopback Mode, the RxD input is

disabled from the external connection and

connected to the TxD output internally

TxD_A

TxD_B

Transmit Data Line Output - This is the transmit

output data line. In the idle state, this signal line is

held in the mark (logic 1) state. During Loopback

Mode, the TxD output is internally connected to the

RxD input