AD-net Technology. CO LTD

- 4 -

www.ad-net.com.tw

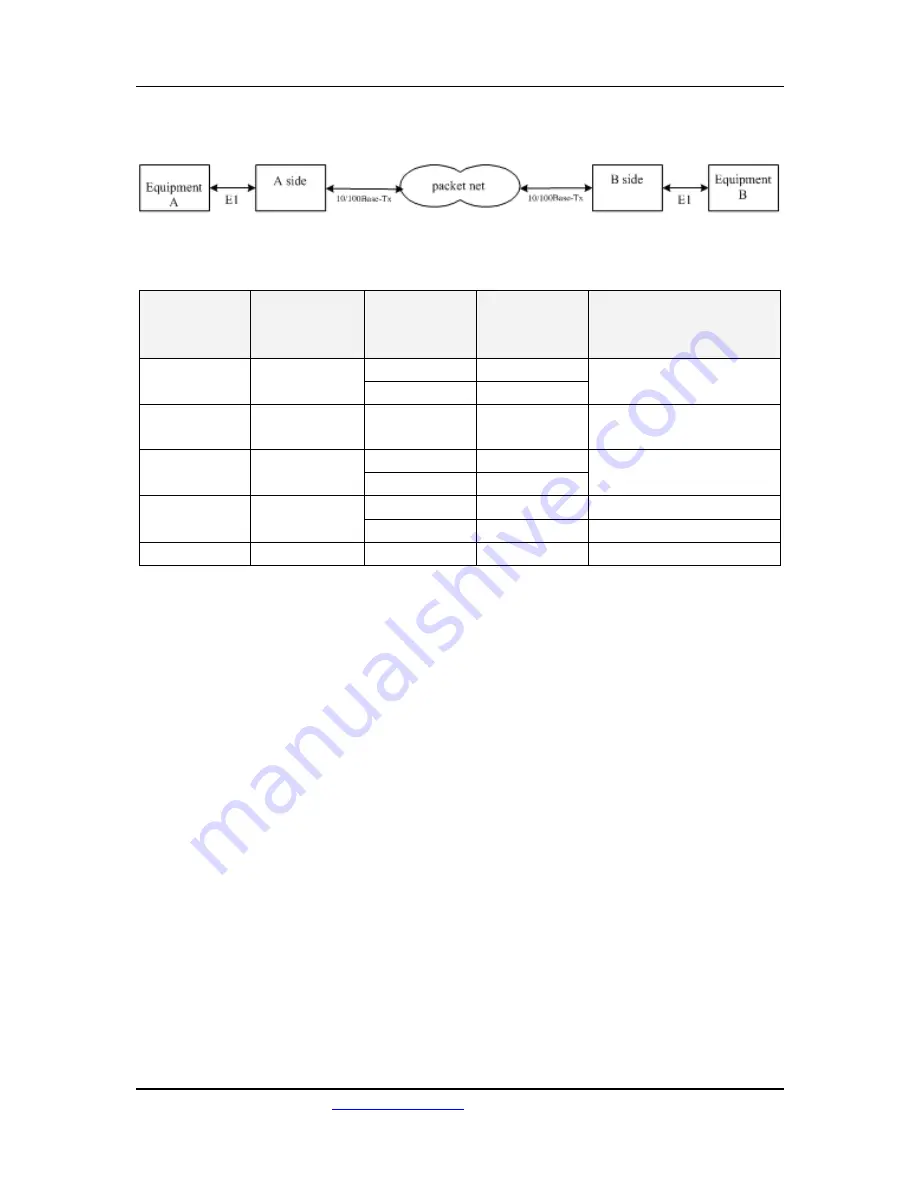

Various timing schemes are listed in Table 1.4-1, for applications depicted in

Fig.1.4-2.

Fig.1.4-2 Timing mode scheme reference diagram

Table 1.4-1 Timing mode schemes

A side

Equipment

clock mode

B side

Equipment

clock mode

A side

AN-TDM-IP

Timing mode

B side

AN-TDM-IP

Timing mode

Note

loop back

loop back

master

master

adaptive

adaptive

Equipment A & B

clocks synchronous

master

master

adaptive

adaptive

Equipment A & B

clocks plesiochronous

loop back

adaptive

master

slave

adaptive

adaptive

adaptive

loop back

slave

master

adaptive

adaptive

slave

slave

Not allowed

2.

System Architecture

2.1

Function Description

The core of AN-TDM-IP-1E1/2E1-A is the TDM/Packet processing unit. It

truncates E1/T1 data stream, and encapsulates the data into Ethernet packet with or

without IP headers. The packets are passed to the Ethernet switch unit via MII

interface, and are sent out through the uplink ports.

In the reverse direction, packets from the uplink ports are sent to the

TDM/Packet processing unit for reassembling the original E1/T1 data stream, and

outputting via E1/T1 interface. TDM/Packet processing unit need to process the

reassembled data to recover the E1 clock which is the key element of the device.

Very sophisticated algorithm is used to ensure that the reconstructed clock will meet

the stringent requirement of TDM applications. The most important parameters are

bit rate, jitter, wander, and signal delay.

The user can modify various operational parameters through Network

Management.

Manuel de l'usager du Mux IP vers 2xE1

www.hypercable.fr