40 Configuring the ICX-250

External DIP Switches

ADCP-62-023

Issue 1, September 1998

© 1998, ADC Telecommunications, Inc.

Note

:

It is recommended that all unassigned channels

be provided an idle termination.

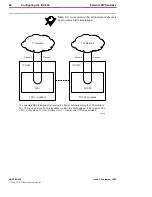

T1 Network

ICX-250

Transmit

Receive

FXS 1

FXS 1 Loopback

T24 Network

ICX-250

Transmit

Receive

FXS 24

FXS 24 Loopback

11276-A

The selected DS0 is looped after leaving the framer before reaching the FXS Interface.

The CPU is used to control this loopback via the Time Slot Assigner (TSA, a part of the

CPU). Subsystems T1 Line Interface Unit, T1 Framer, and CPU are exercised.