Registers

23

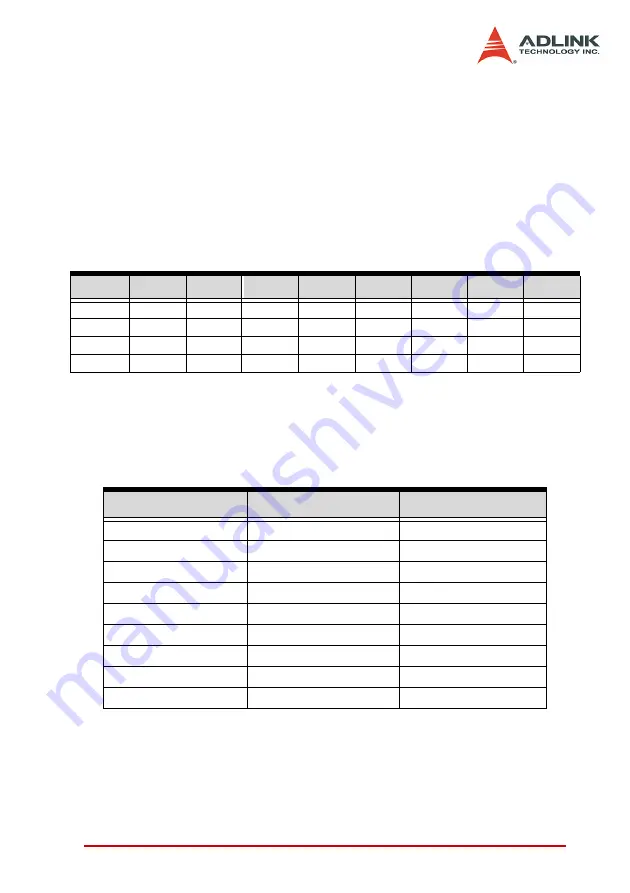

4.5 Trigger Level Register

The trigger condition of PCI-9812/10 includes trigger level and

trigger slope. This register sets the trigger level, and the trigger

source register described in the next paragraph sets the trigger

slope.

Address:

BASE + 0ch

Attribute:

write only

Data Format:

TRGLVL7..0: trigger level

---: Any value

Relationship between the 8-bit trigger level and the trigger voltage:

Bit

7

6

5

4

3

2

1

0

BASE+Ch TRGLVL7 TRGLVL6 TRGLVL5 TRGLVL4 TRGLVL3 TRGLVL2 TRGLVL1 TRGLVL0

BASE+Dh

---

---

---

---

---

---

---

---

BASE+Eh

---

---

---

---

---

---

---

---

BASE+Fh

---

---

---

---

---

---

---

---

TRGLVL7..0(bit 7..0)

Trigger voltage(

±

1V)

Trigger voltage(

±

5V)

0xFF

0.992V

4.96V

0xFE

0.984V

4.92V

|

|

|

0x81

0.008V

0.04V

0x80

0.000V

0.00V

0x7F

-0.008V

-0.04V

|

|

|

0x01

-0.992V

-4.96V

0x00

-1.000V

-5.00V

Table 4-3: Relationship between 8-bit trigger level and trigger voltage

Summary of Contents for NuDAQ PCI-9810

Page 4: ......

Page 10: ...vi ...

Page 19: ...Installation 9 2 3 PCI 9812 10 s Layout Figure 2 1 PCB Layout of the PCI 9812 10 ...

Page 22: ...12 ...

Page 40: ...30 ...

Page 78: ...68 Software Utility ...