LEC-

iMX8M plus User’s Guide 1.0

SGET SMARC Rev 2.1

Page 31

copyright © 2021 ADLINK Technology Inc.

4.3.6

PCIe Ports

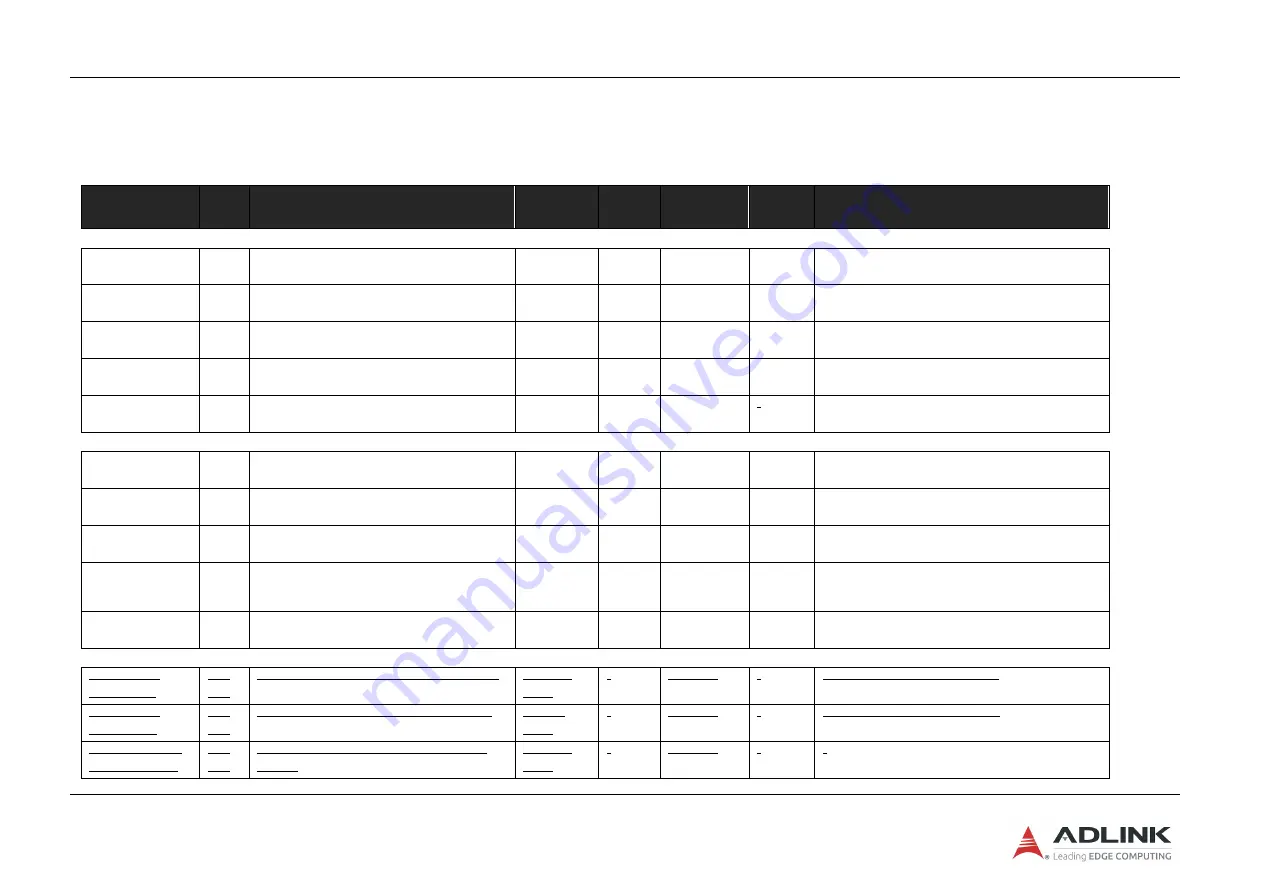

The module supports two PCIe Gen 2.1 ports (PCIE_A and PCIE_B).

Name

Pin # Description

I/O

Type

I/O

Level

Power

Domain

PU / PD Comments

PC

PCIE_A_TX-

P89

P90

Differential PCIe link A transmit data pair

O LVDS

PCIE

Runtime

Series AC coupled on module

PC

PCIE_A_RX-

P86

P87

Differential PCIe link A receive data pair

I LVDS

PCIE

Runtime

Series AC coupled off module

PCIE_

PCIE_A_REFCK-

P83

P84

Differential PCIe Link A reference clock

output

O LVDS

PCIE

Runtime

PCIE_A_RST#

P75

PCIe Port A reset output

O

CMOS

3.3V

Runtime

PCIE_A_CKREQ#

P78

PCIe Port A clock request

I OD

CMOS

3.3V

Runtime

No need for this signal because module

provides onboard PCIe clock

PC

PCIE_B_TX-

S90

S91

Differential PCIe link B transmit data pair

O LVDS

PCIE

Runtime

Series AC coupled on module

PC

PCIE_B_RX-

S87

S88

Differential PCIe link B receive data pair

I LVDS

PCIE

Runtime

Series AC coupled off module

PCIE_

PCIE_B_REFCK-

S84

S85

Differential PCIe Link B reference clock

output

O LVDS

PCIE

Runtime

PCIE_B_RST#

S76

PCIe Port B reset output

O

CMOS

3.3V

Runtime

PCIE_B_CKREQ#

P77

PCIe Port B clock request

I OD

CMOS

3.3V

Runtime

No need for this signal because module

provides onboard PCIe clock

PC

PCIE_C_TX-

S81

S82

Differential PCIe link C transmit data pair

O LVDS

PCIE

Runtime

Series AC coupled on module

PC

PCIE_C_RX-

S78

S79

Differential PCIe link C receive data pair

I LVDS

PCIE

Runtime

Series AC coupled off module

PCIE_

PCIE_C_REFCK-

P80

P81

Differential PCIe Link C reference clock

output

O LVDS

PCIE

Runtime

Summary of Contents for SMARC NXP i.MX8M-plus Quad NPU

Page 1: ...LEC IMX8MP 02 01 2021...