40

Table 4-15

shows how to set the counter INT. The Counter INT state

register is the read-only register. When Bit0 is “1”, the counter’s

interrupt has occurred. To clear the interrupt of counter, users can

write any value (including “0”) to the Clear INT register. The Clear

INT register is write-only register and has the same address as the

INT State register.

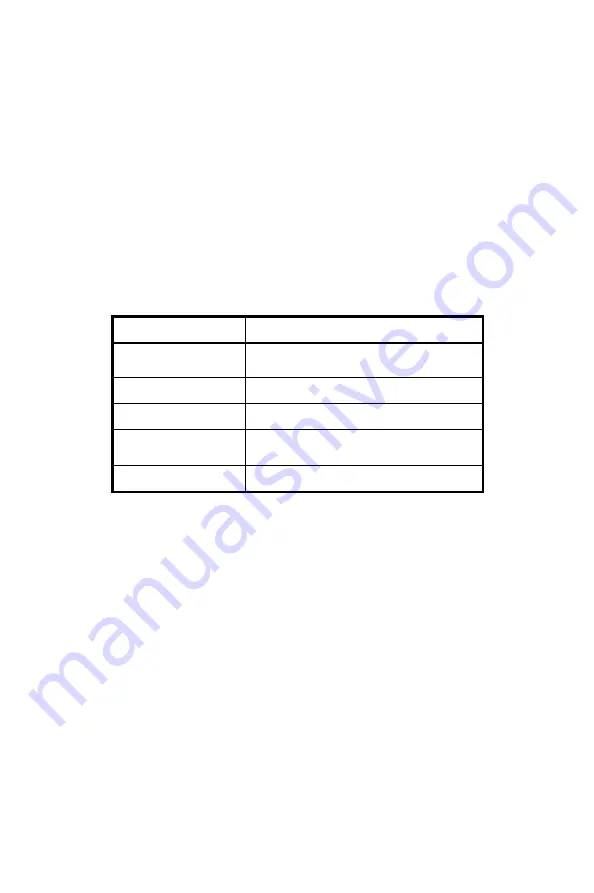

Table 4-15 INT Register of Counter

Output Control

Counter mode bits CM 4 and CM 5 specify the output control

configuration. (Refer to register format) select the active output type:

Digital output, Counter output TC, or TC Toggle from low output

waveforms.

One output form available is called Terminal Count (TC) and

represents the period in time that the counter reaches an equivalent

value in the Set Value Register (Base Add. + 18h). The TC width is

determined by the period of the counting source. The TC will be

INT State Register

Base Add.+ 16h

(Read Only)

Bit 0

Abbreviation

INT

Clear INT Register

Base Add.+ 16h

(Write Only)

Bit15~0

Abbreviation

Any value

Summary of Contents for MIC-3756

Page 2: ...ii This page is left blank for hard printing ...

Page 7: ...1 Introduction 1 CHAPTER ...

Page 8: ...2 This page is left blank for hard printing ...

Page 13: ...7 Hardware Configuration CHAPTER 2 ...

Page 14: ...8 This page is left blank for hard printing ...

Page 20: ...14 2 3 Board Layout Fig 2 1 MIC 3756 board layout ...

Page 22: ...16 This page is left blank for hard printing ...

Page 23: ...17 Pin Assignment and Jumper Setting CHAPTER 3 ...

Page 24: ...18 This page is left blank for hard printing ...

Page 26: ...20 Fig 3 1 I O Connector pin assignments for the MIC 3756 ...

Page 33: ...27 Operations CHAPTER 4 ...

Page 34: ...28 This page is left blank for hard printing ...

Page 49: ...43 Appendixes ...

Page 50: ...44 This page is left blank for hard printing ...

Page 56: ...50 Note Write 1 to the bit Fn in Interrupt Control Register clears the interrupt ...