The E5 series Xeon processors support cache memory as listed below:

A 32-KB instruction and 32-KB data first-level cache (L1) for each core.

A 256-KB shared instruction/data mid-level (L2) cache for each core.

Up to 20 MB last level cache (LLC): up to 2.5 MB per core instruction/data last level

cache (LLC), shared among all cores.

2.2.2 Platform Controller Hub (PCH)

An Intel® C604 provides the peripheral connection in the Intel® Sandy Bridge

platform. It contains DMI Gen2, 8x PCIe Gen2 root ports, 2x SATA 6Gb/s, 4x SATA

3Gb/s, 4x SAS 3Gb/s, 14x USB 2.0 and supports one internal GbE MAC. For more

details, please refer to section 2.3.

2.2.3 DMI Gen2

Direct Media Interface (DMI) is the chip-to-chip connection between the processor

and PCH. This high-speed interface integrates advanced priority-based servicing

allowing for concurrent traffic and true isochronous transfer capabilities. Base

functionality is completely software transparent permitting current and legacy software

to operate normally. New for C604 chipset, the DMI interface operates at 5.0 GT/s.

2.2.4 PCI Express Port Configuration

Intel® Xeon® E5-2600 series processors support 40 PCI Express Gen3 ports. They

are configured to two x16 ports, one x8 port and five x4 ports in the MIC-5332. The

PCI Express interface is connected to RTM (Port1 and 2) and update channel (Port 3,

optional).

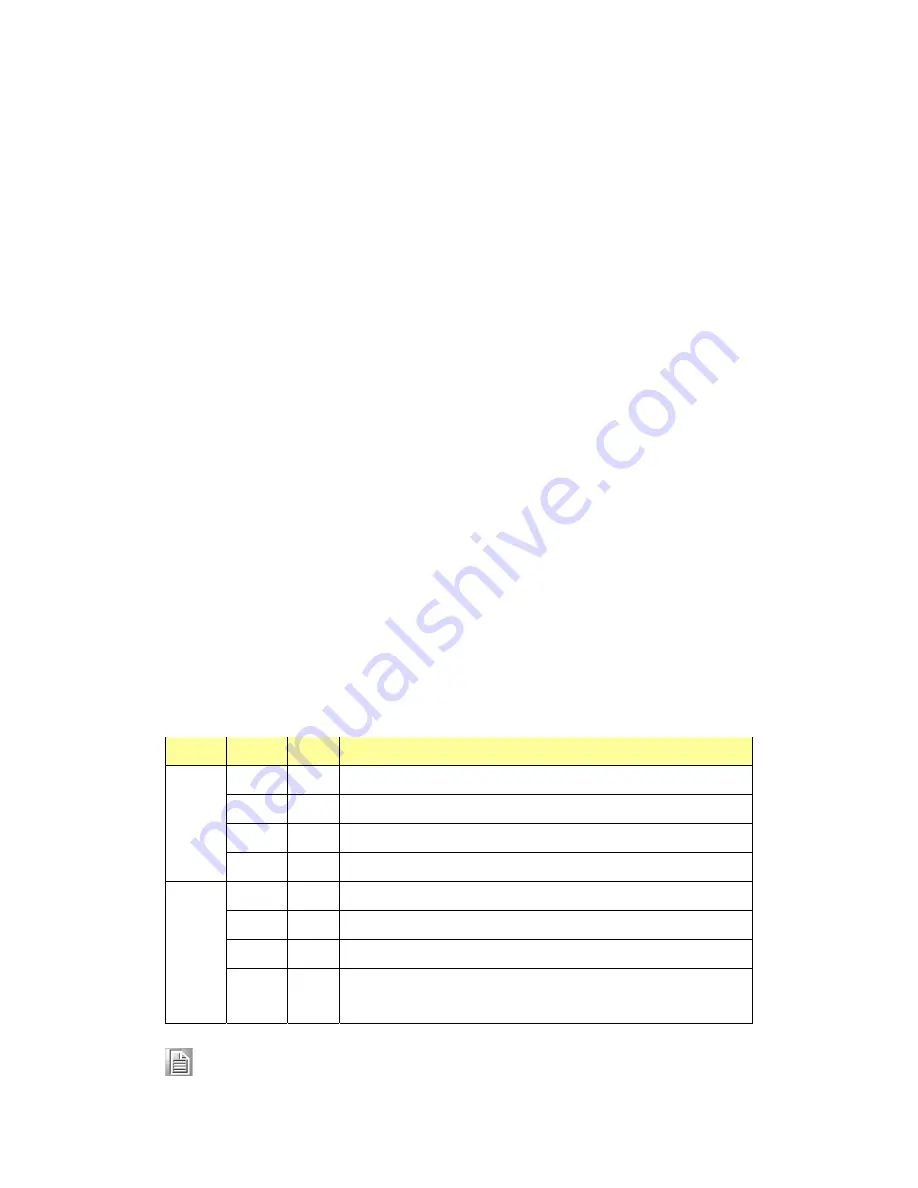

CPU Port No. Width

Description

0

0

x4

Connection for DMI between the CPU and PCH

1

x4

Base Interface and I/O Control, connected to Intel® i350-AM4

2

x8

Fabric Interface, connected to Intel® i82599 10GbE controller

3

x4

For update channel, connected to Zone 2 (optional)

1

0 x4

Not

connected

1

x4

For RTM use, connected to Zone 3

2

x16

For RTM use, connected to Zone 3

3 x16

connected to fabric mezzanine (FMM); configurable as 1x16 or

2x8

Table 2.3 PCI Express Port Configuration on the MIC-5332

1.

Note

:

Summary of Contents for MIC-5332

Page 7: ...This page is left blank intentionally ...

Page 10: ...Chapter 1 Product Overview This chapter briefly describes the MIC 5332 ...

Page 15: ...Chapter 2 Board Features This chapter describes the MIC 5332 hardware features ...

Page 43: ...Figure 3 10 Jumper Locations JP1 JP5 JP6 ...

Page 44: ...Chapter 4 Hardware Management This chapter describes the IPMC firmware features ...

Page 105: ... root localhost ipmitool raw 0x2E 0x40 0x39 0x28 0x00 0x03 0x01 section ...

Page 108: ...Appendix A IPMI PICMG Command Subset Supported by IPMC ...

Page 120: ...33 48V_A 48V input feed A 34 48V_B 48V input feed B ...