PCI-1243U User Manual

52

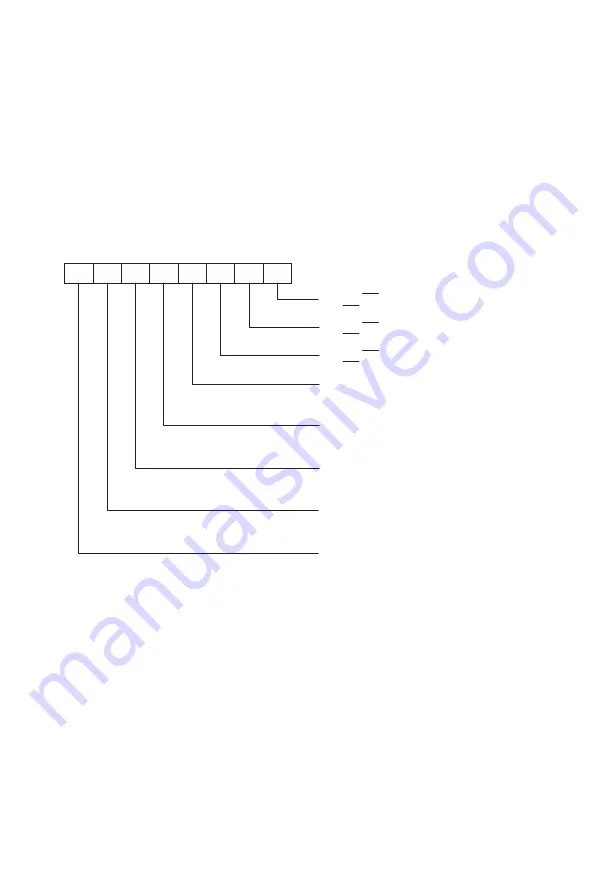

The definitions of Status registers are as following:

4.4.1 Status0: Channel Status Buffers (RD0, RD4, RD8

and RD13)

There is a status buffer for each channel (status 0). These buffers are

found at BASE +0, BASE +4, BASE +8 and BASE +13 for channel 1,

channel 2, channel 3 and channel 4 respectively. These buffers enable

you to read the internal status of each channel, and also get certain infor-

mation on input signals or conditions.

4.4.2 Extension Monitor

When the Extension Monitor was selected, you can check the value of

each register R0 ~ R7 by assigning the register with “register selection

command”, and then read the specific address respectively. Also, Status1,

Status2 and Status3 can be read in the extension monitor mode. On the

following page are the definitions of each status register.

7

6

5

4

3

2

1

0

Monitor INT output when operation is stopped

0: INT is being output

Status 0 bit configuration

Monitor INT output at ramping-down point

0: INT is being output

Monitor INT output at external start

0: INT is being output

Operation status

0: Stopped

1: Operating

Pulse output zero status

0: Non zero

1: Zero

Pulse counter and R5 comparison

0: Pulse counter > R5

1: Pulse counter <= R5

Monitor acceleration status

0: Not accelerating

1: Accelerating

Monitor deceleration status

0: Not decelerating

1: Decelerating

Summary of Contents for PCI-1243U

Page 1: ...PCI 1243U 4 Axis Stepping Motor Control Card User Manual ...

Page 8: ...PCI 1243U User Manual viii ...

Page 14: ...PCI 1243U User Manual 6 ...

Page 35: ...27 Chapter3 Figure 3 8 Point to Point Movement ...

Page 38: ...PCI 1243U User Manual 30 ...

Page 80: ...PCI 1243U User Manual 72 Appendix A Diagrams A 1 Jumper and Switch Layout ...

Page 82: ...PCI 1243U User Manual 74 ...

Page 88: ...PCI 1243U User Manual 80 ...